由于大型SoC芯片中包含特别多的子模块,IP,而且各个模块的规模也比较大。此时如果一开始就过整芯片的LVS肯定是过不掉的,而且runtime还特别久。

物理验证Calibre LVS Stamping Conflict SoftConnect案例解析

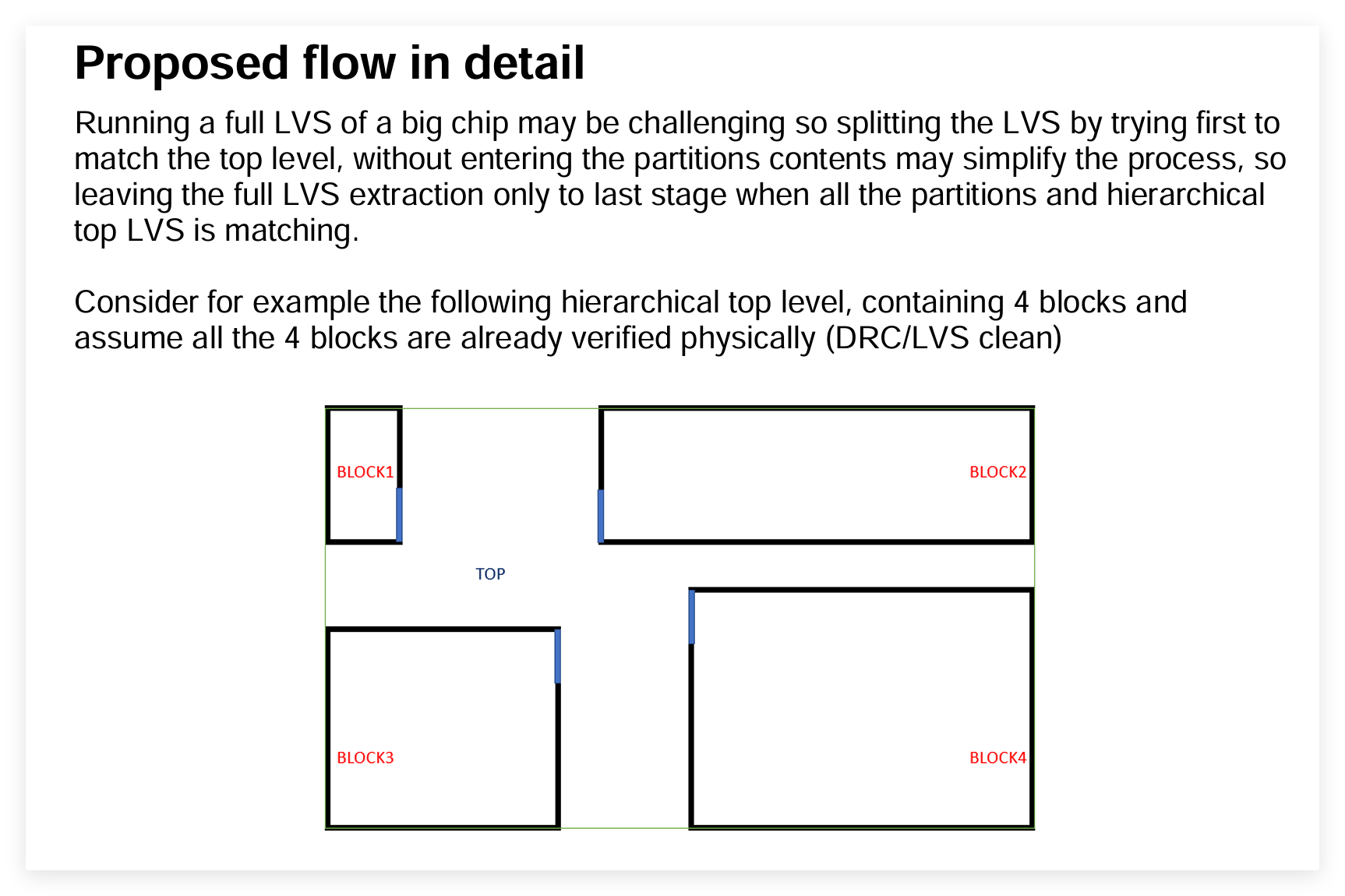

一般我们SoC Top Hierarchical Flow实现的LVS可以这么做:

1)先过掉顶层Top only的LVS

此时各大模块Block,IP的GDS和CDL都仅仅包含接口相关信息和各个模块的PG信息。这样这些模块和IP的GDS就不会特别大,而且此时根本不用关心模块内部的LVS是否过掉。

关于如何根据LEF文件来生成简易GDS和CDL的教程,可以查看下面这份教程。

2)各个子模块的LVS过掉

3)顶层Top分批次带上真实的Block GDS和CDL来做LVS

这个阶段主要排除顶层Top和子模块接口相关short,open带来的LVS问题

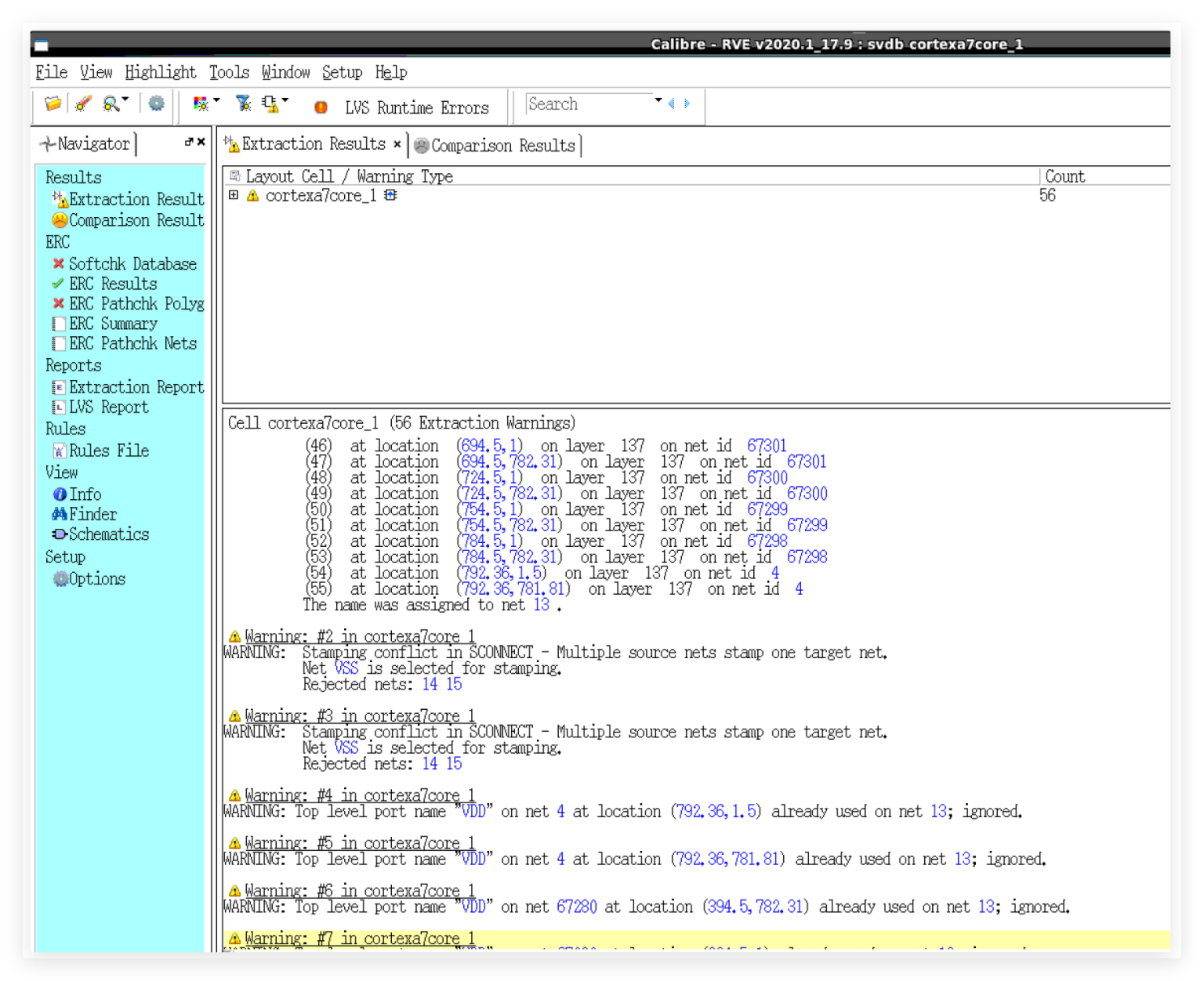

在这个阶段对于子模块设计中存在PG open和信号线short问题,我们可以skip掉,因为我们会把这些模块当做bbox来处理。

这些问题也会体现在Calibre LVS GDS抽取报告中,但它不影响当前顶层top的LVS结果。

4)顶层Top全部Flatten LVS

下面分享Cadence官方提供的一个Hierarchical LVS for large hierarchical designs 教程。其基本原理和处理方法和咱们一直分享的方法类似。

物理验证Calibre LVS | SMIC Process过LVS时VNW和VPW要如何做处理?