各位不知道有没有遇过,一对很长的差分走线,看起来很正常,但是测试结果偶尔会fail偶尔会pass,不像是软件问题,也不像是制程问题。 看了一下Layout,发现阻抗匹配控制的非常好,TDR测试也显示阻抗好棒棒,虽然线是长了点,但是损耗还是有不少Margin。 那... 为什么会有问题?

如果您遇到过,那恭喜您,这应该是PCB玻璃纤维造成的Intra-Pair Skew,而导致差动对P/N两条线有着时间差。 在差动对的理论基础上,开宗明义就有提到,两条线必须等长,或说是相等时间差,才会是完美的差动讯号。 如果这个时间差,或说是delay,两两不一致,则所引起的讯号损耗会变的过大以及产生难以控制的共模效应(Common-mode)。

本周,我们来看看何谓Differential Pair Intra-Pair Skew,这个Skew到底是怎样影响我们的通道设计!

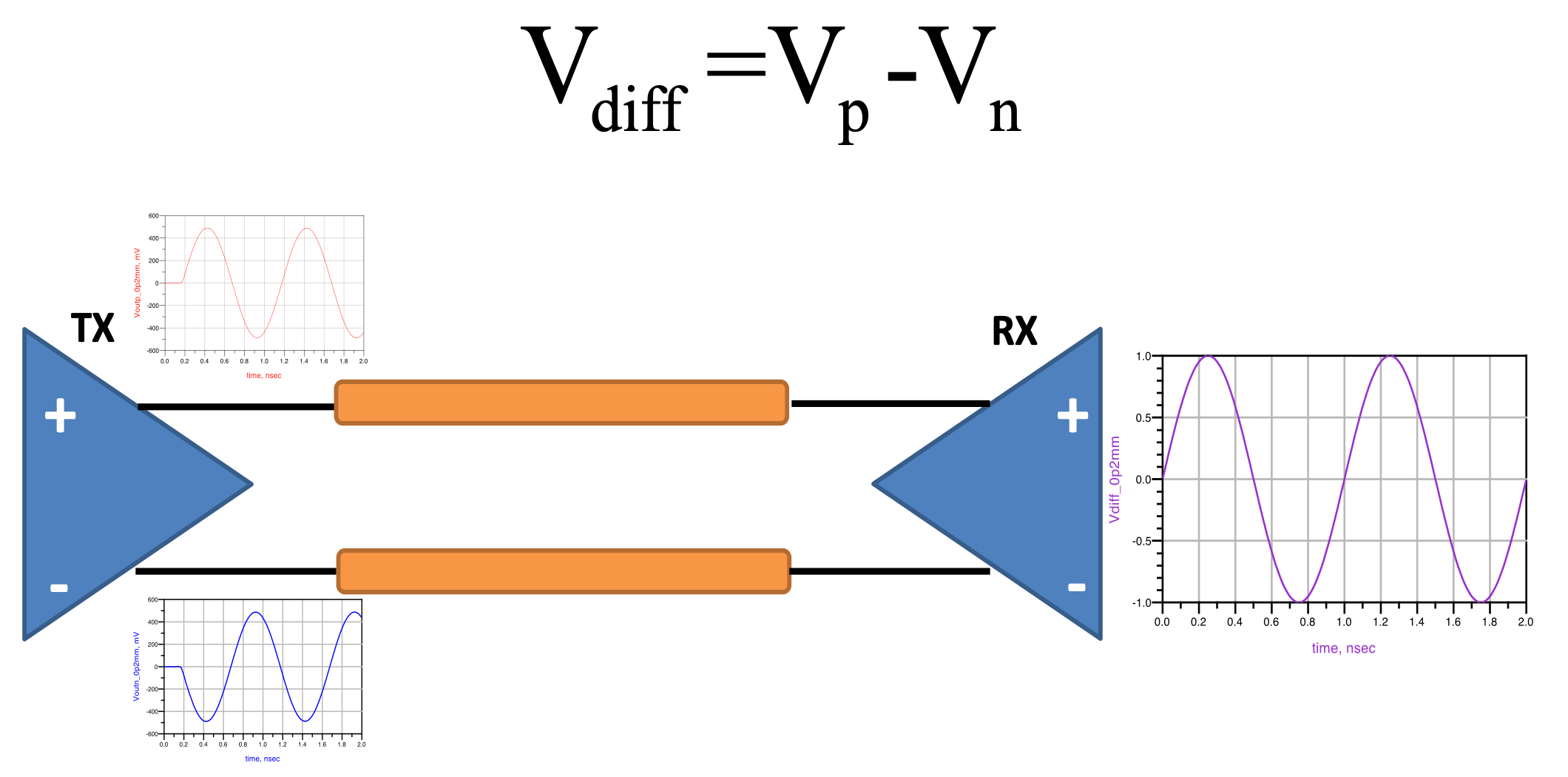

回顾一下差动对理论

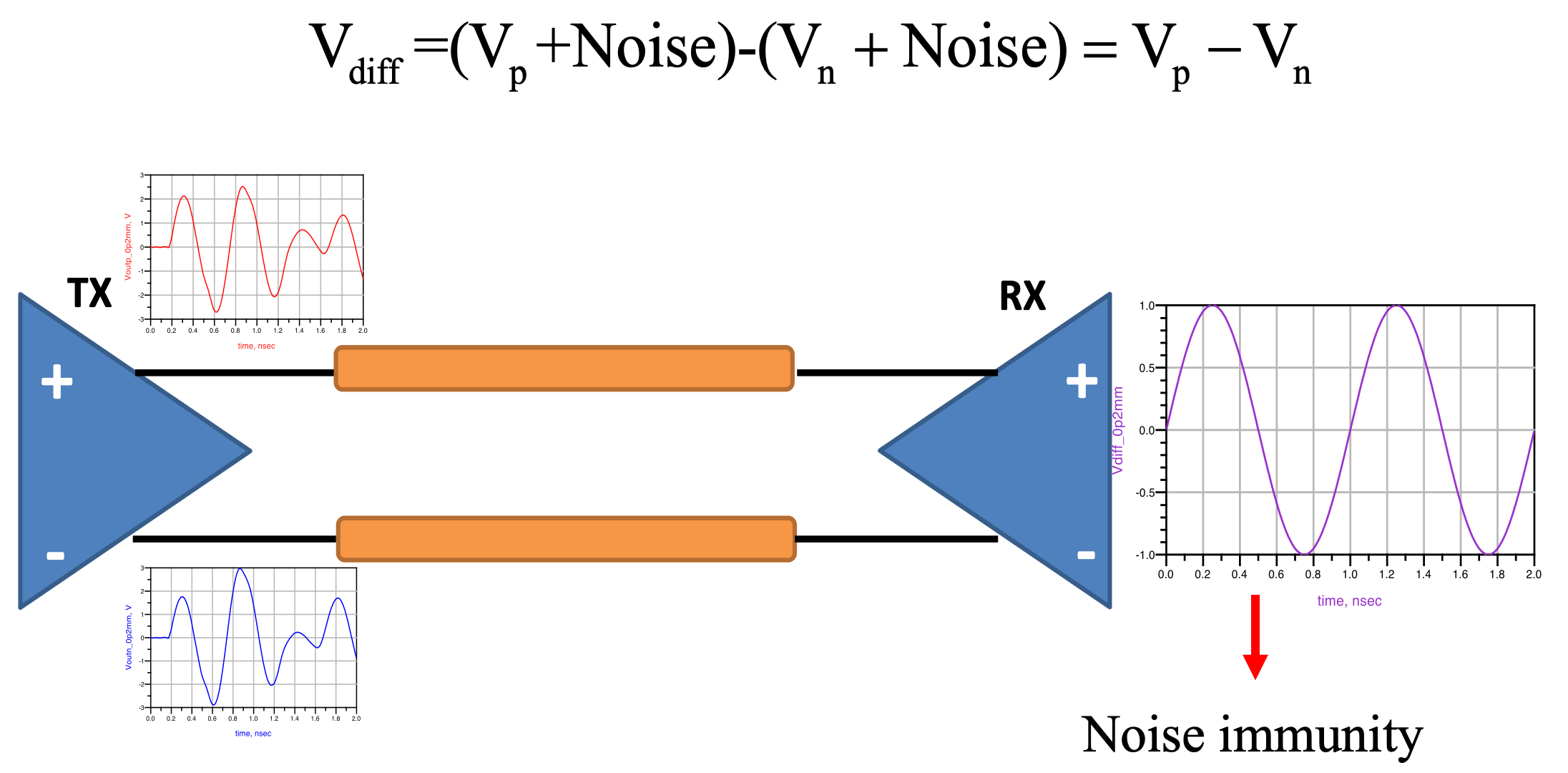

在高速信号传输的设计中,差动对(Differential Pair)是一种非常常见的走线方式,这种走线方式虽然牺牲的一倍的走线面积,但是换来对于高速信号干扰的抵抗性。 而要达到一个良好的差动对设计,「等长」这件事几乎是SI与Layout两个团队的基本功。 那到底为什么差动对要等长? 原

Differential Intra-pair skew,指的就是在差动对里,正负讯号线之间出现的「延迟时间差」。 差动对是两条走线成对一起运作,传输同一组讯号,不过一条走的是正讯号,另一条则是相反方向的负讯号。 这两条信号必须保持高度同步,才能在接收端被正确还原回原始信号。 简单来说,原本应该同时到达的两条讯号线,却有人先跑、有人后到,这种「步调不一致」就叫做 skew。 在高速数据传输中,哪怕只是微小的延迟偏移或是讯号的「错开」,都可能左右讯号的完整性。

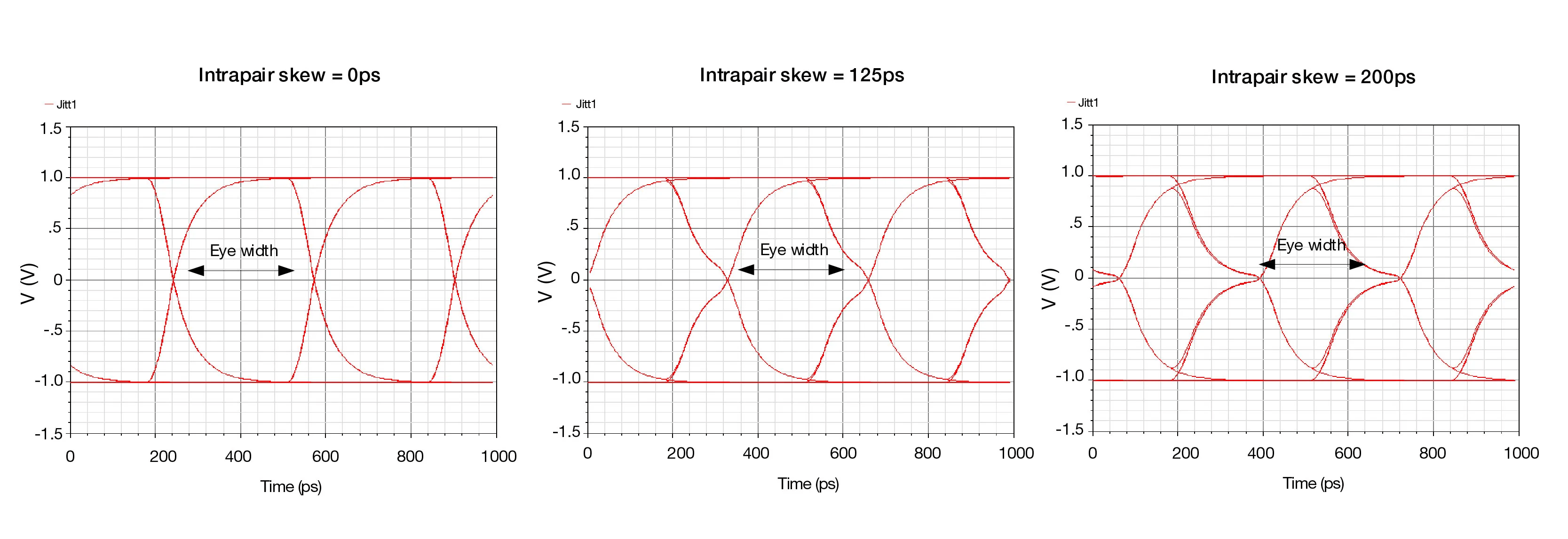

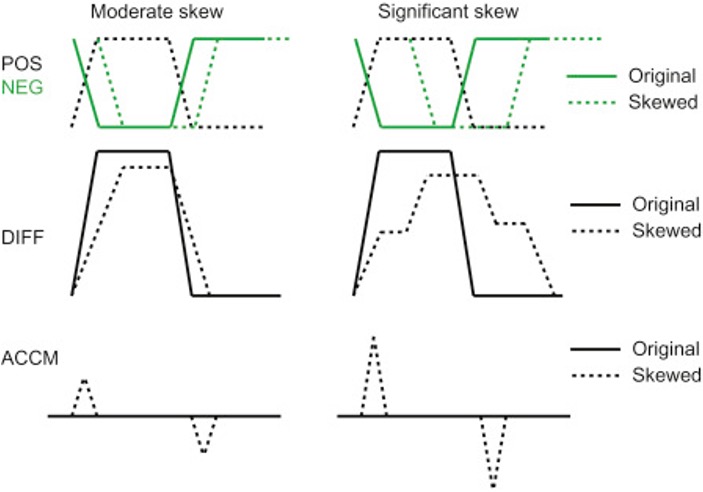

当Skew变大时,讯号波形的形变也会变得更严重!

当Skew越来越大时,眼图随之变差!

发生Intra-Pair Skew造成的状况

Intra-Pair Skew发生时,会有以下几个负面影响:

- 损耗变大,产生高频谐振点

- 产生共模效应,降低差动特性

- 随着Data Rate上升,Skew对于UI占比越来越大,导致讯号严重失真

以下我们一个一个来解析!

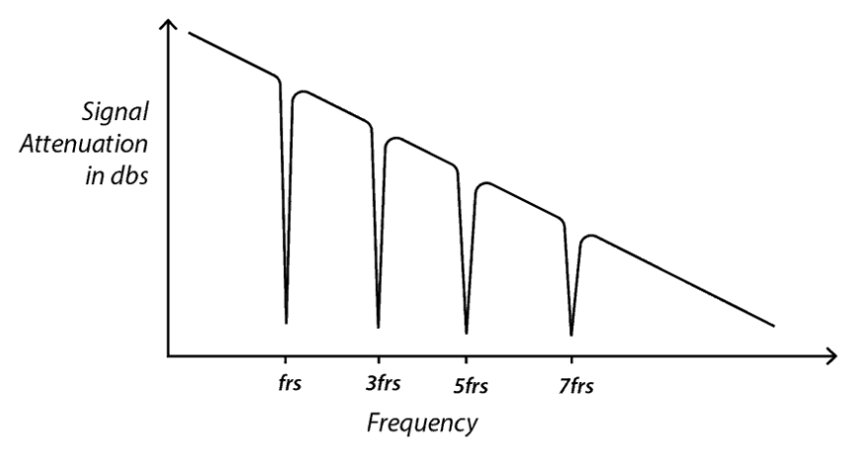

Skew使得高频损耗变的更严重

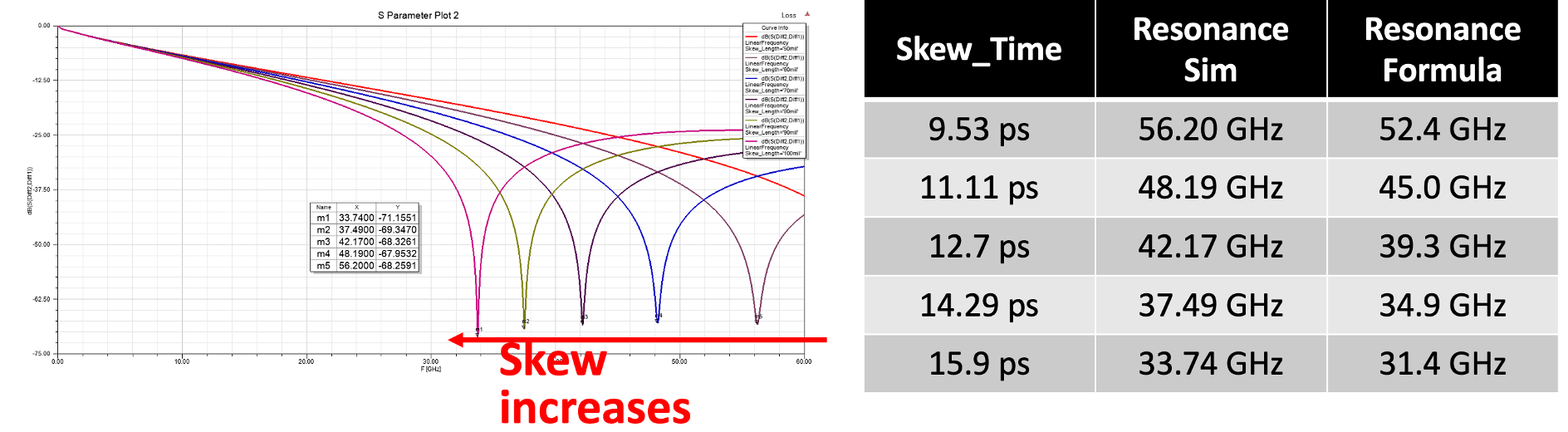

Skew会带来高频谐振,如果要知道对于损耗的影响范围,我们可以来计算这个谐振点的发生频率:

首先,我们先假设一个复数传输函数H(f)

H(f)=|H(f)|ejθ(f)

其中,|H(f)|表示DUT的幅度响应,而θ(f)则为其相位响应。

相位响应可以进一步定义为:

θ(f)=−2π×f×Δt(f)

这里的Δt(f)是传输函数的相位延迟,因此可以根据相位响应直接反推得到相位延迟:

Δt(f)=−θ(f)2πf

而我们就可以得到这个谐振频率点:

f=12Δtpd

也就是说,Skew越小,谐振点就越高频,且这个谐振点会在奇数倍数频率出现,假设1GHz有谐振点,则3GHz、5GHz、7GHz也会出现谐振点。

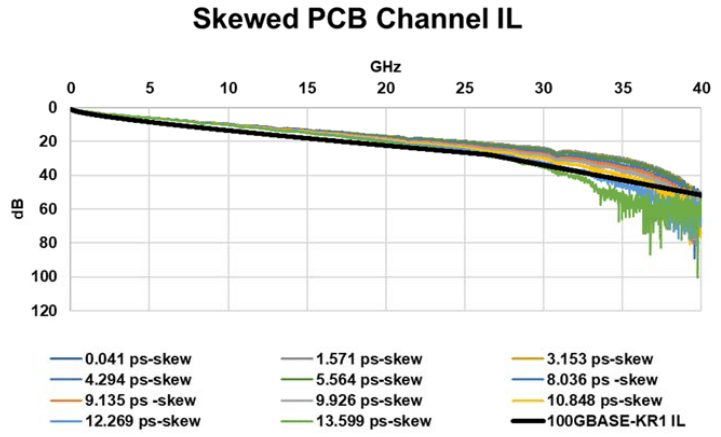

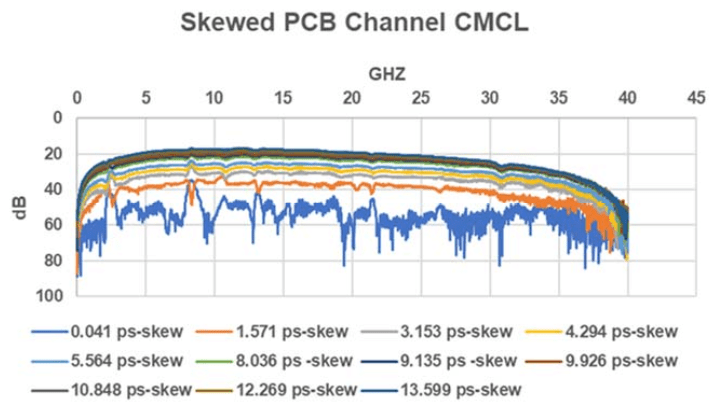

接着我们可以通过这个公式,计算不同Skew时间下,谐振点的频率,并与实际SI模拟的频率点做比对看看这个公式有没有效。 可以发现,公式与模拟的谐振频率,大概差了7%,公式计算得到的频率会较低一些,但是整体而言还算可以接受!

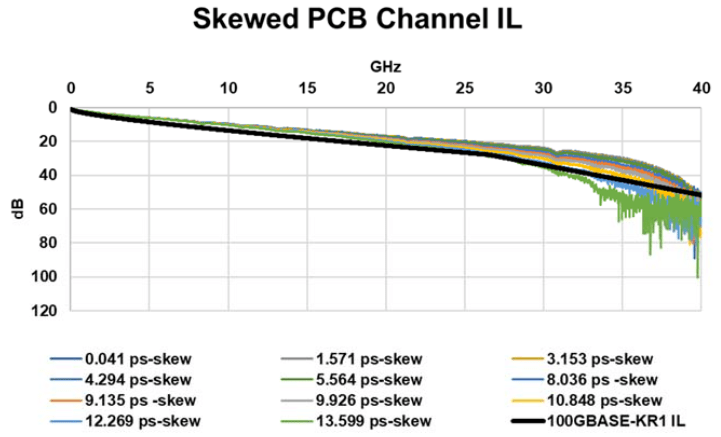

从实测的结果我们也可以发现这不是纸上谈兵,一个10G-KR的通道,原本设计的Loss好好的,可以通过这条黑色的Spec,可是当我们刻意将skew调整至13ps(两条线大约差70mil),Loss在30GHz之后直接往下跑,超出Spec,以我们的计算12.7ps大约是42GHz,从这个实测结果来看,应该是可以对得上的对吧!

Skew导致Common-Mode Noise上升

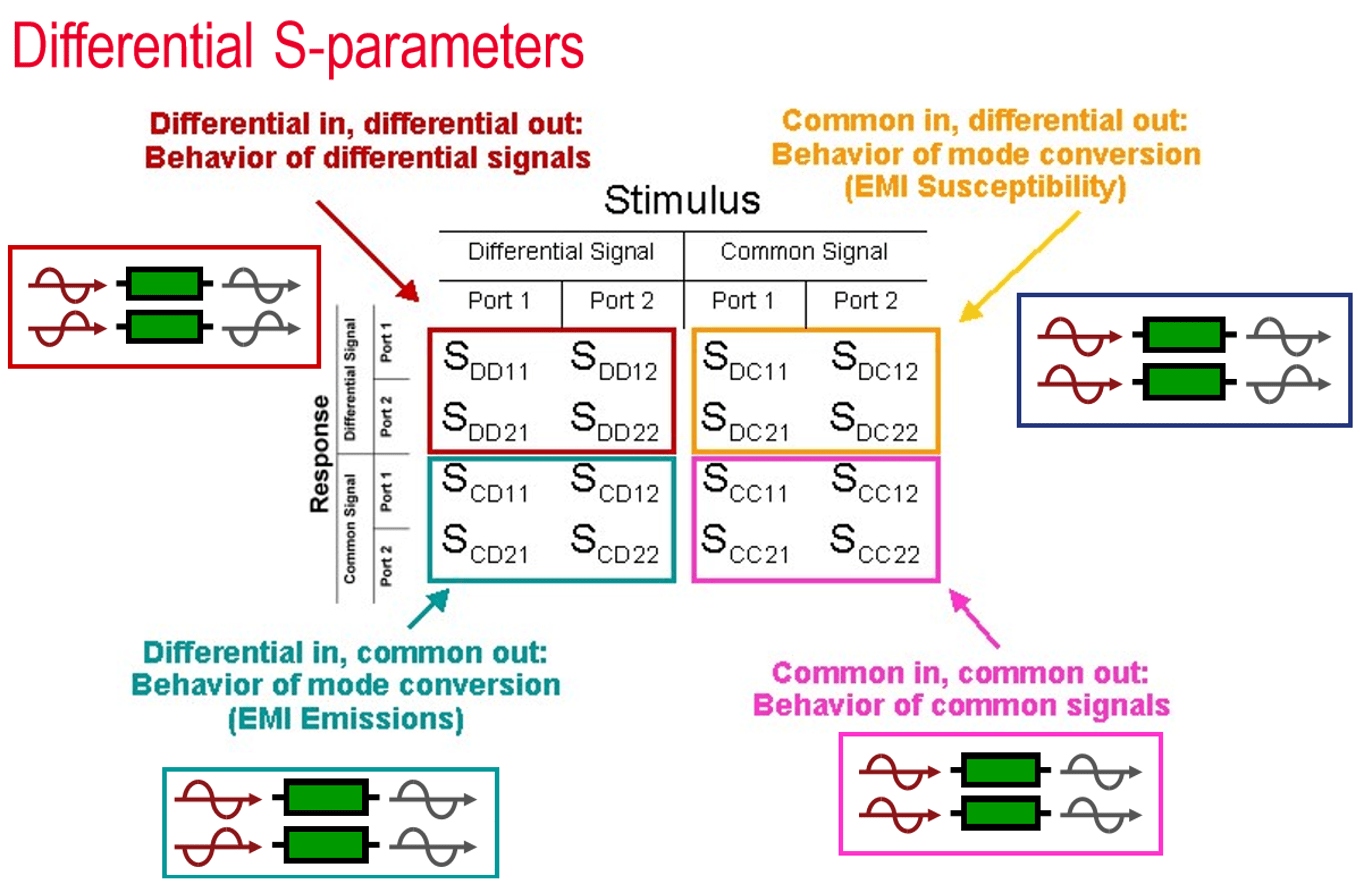

我们在看系统级的差动对特性时,最先关注的通常是Differential Return Loss(Sdd11)和Differential Insertion Loss(Sdd21),再来可能根据Crosstalk是否严重而去关注Sdd31 and Sdd41,比较少会去关注共模特性。

P.S. 如果是Connector与Cable厂商则例外,这些零组件牵扯到对机台外部的连接,可能会有EMI的问题,因此对于共模很关注。 一些规范也都有针对这些零部件有Scd的要求。

可是其实Common-mode noise是非常重要的。 我们可以从Scd这个参数来判断,到底这个通道设计有多少的不平衡(unbalance)效应。 越大的Unbalance,表示越多的Common-mode noise,表示这个差动对设计越不好,通常表示的是Skew越大!

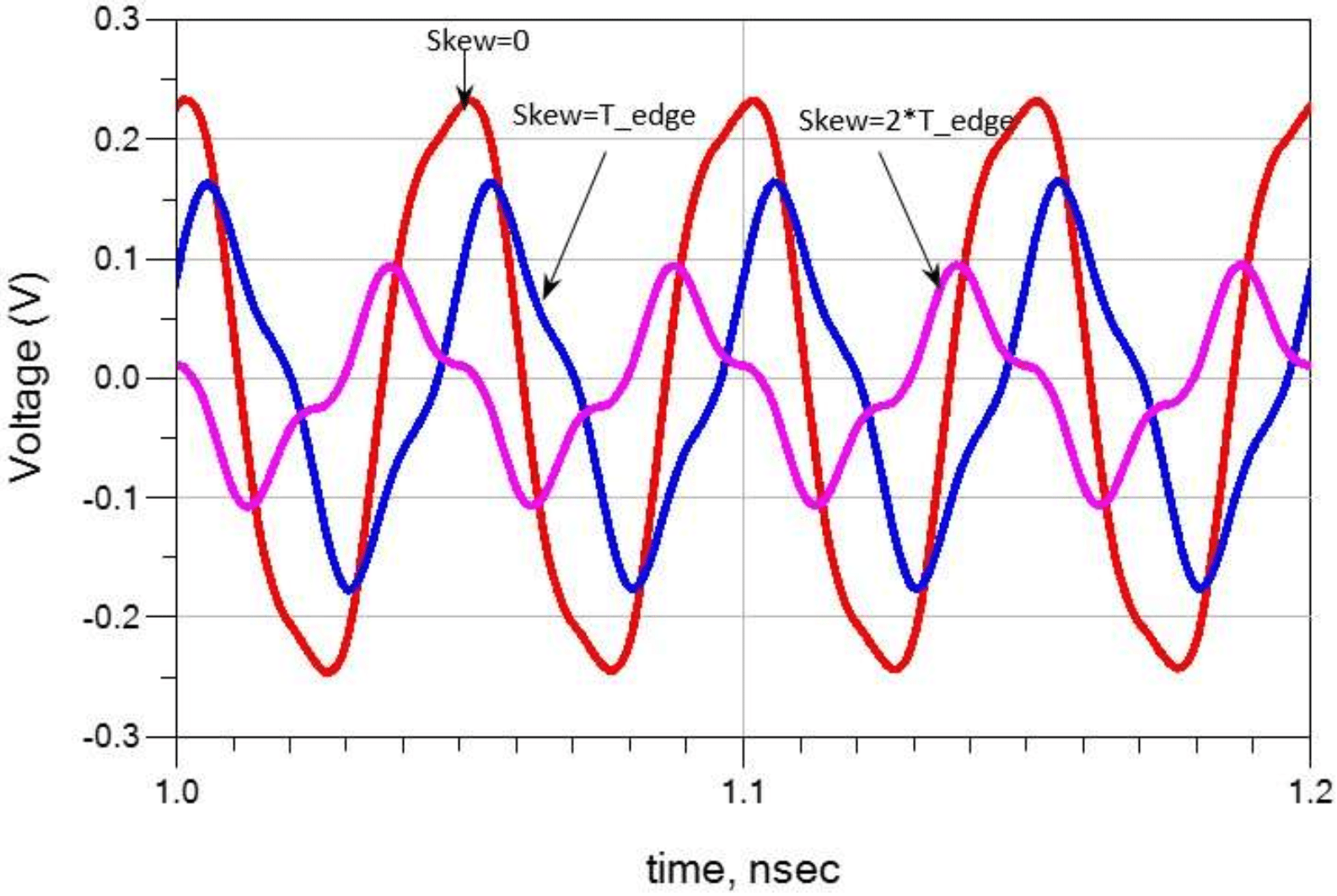

从这张图可以清楚地看出,Common-mode noise(ACCM)会随Skew变大而变大:

一样透过实测数据让大家对于Skew造成的负面性应更加明了,Skew越大则Common-mode noise越惨呀!

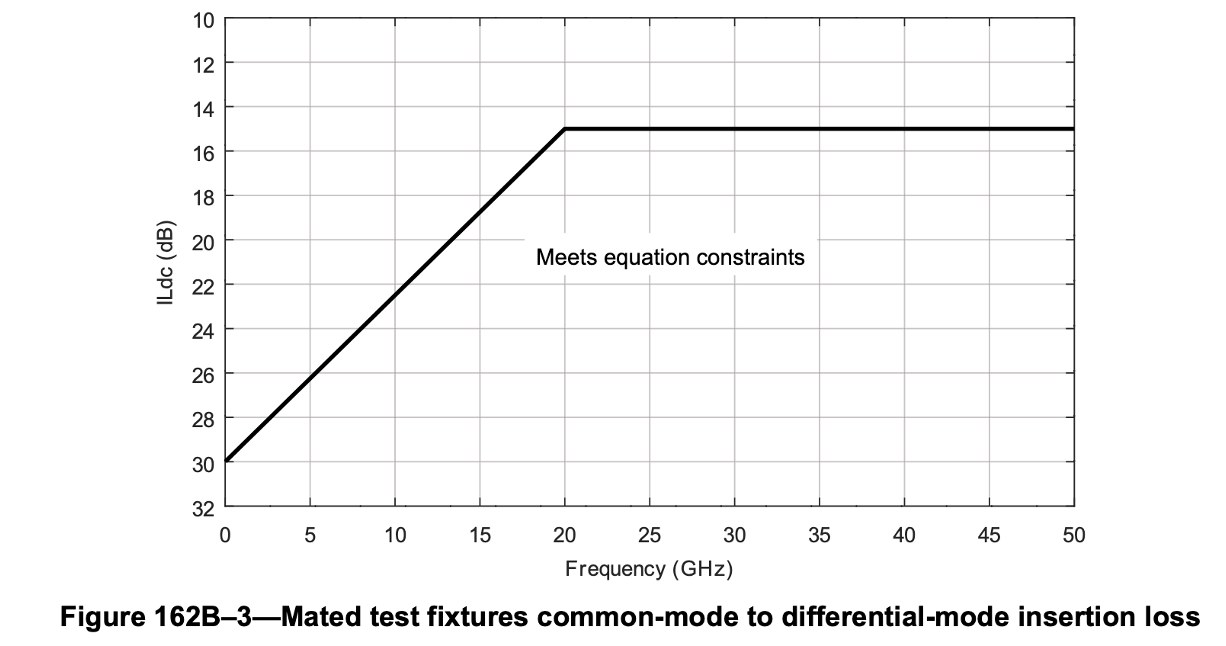

IEEE 802.3ck针对MTF(Mated Test Fixture)的Scd(与Sdc相同)的规范:

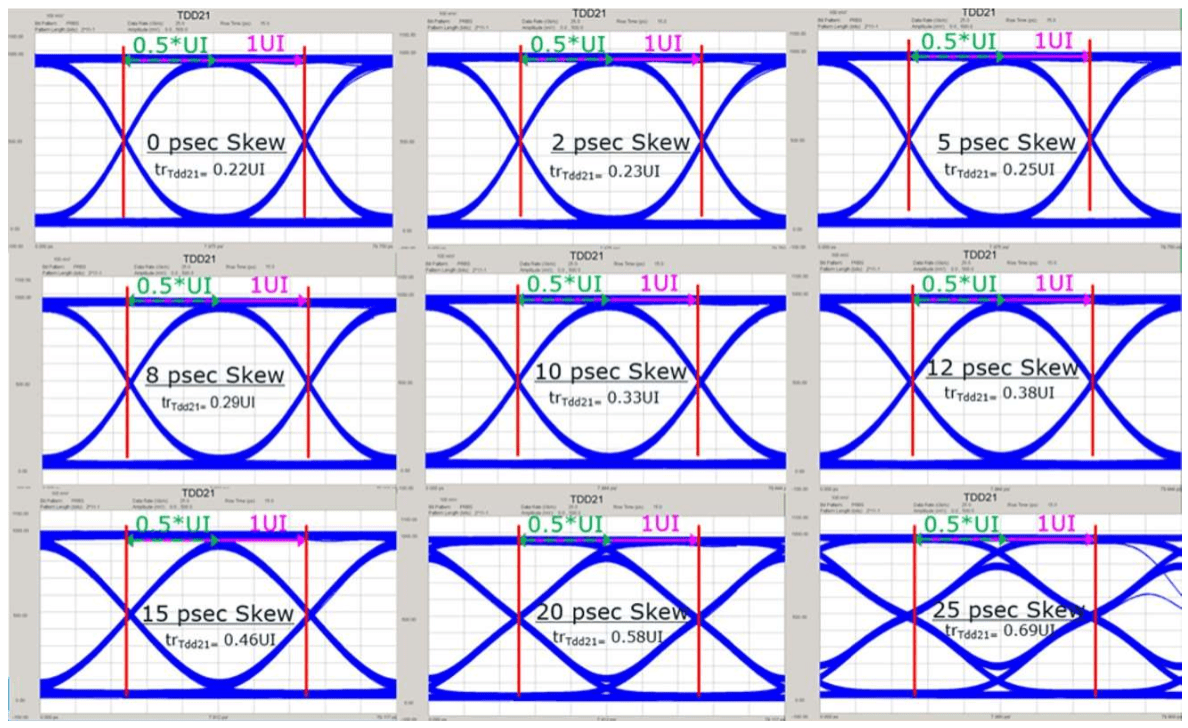

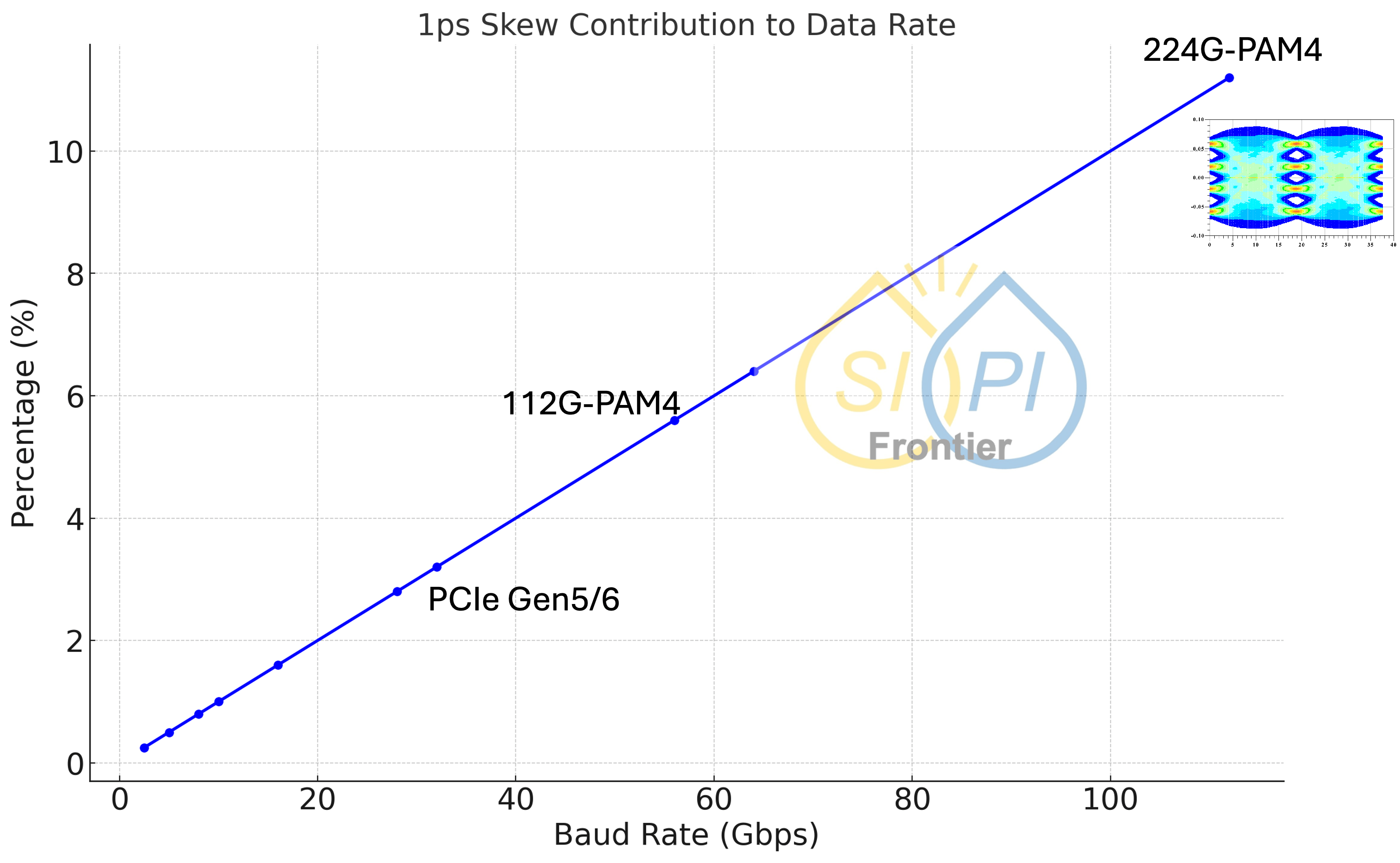

Skew的时间占比随着Data Rate变快,而越来越大

最后,我们简单讨论下时序方面的问题。

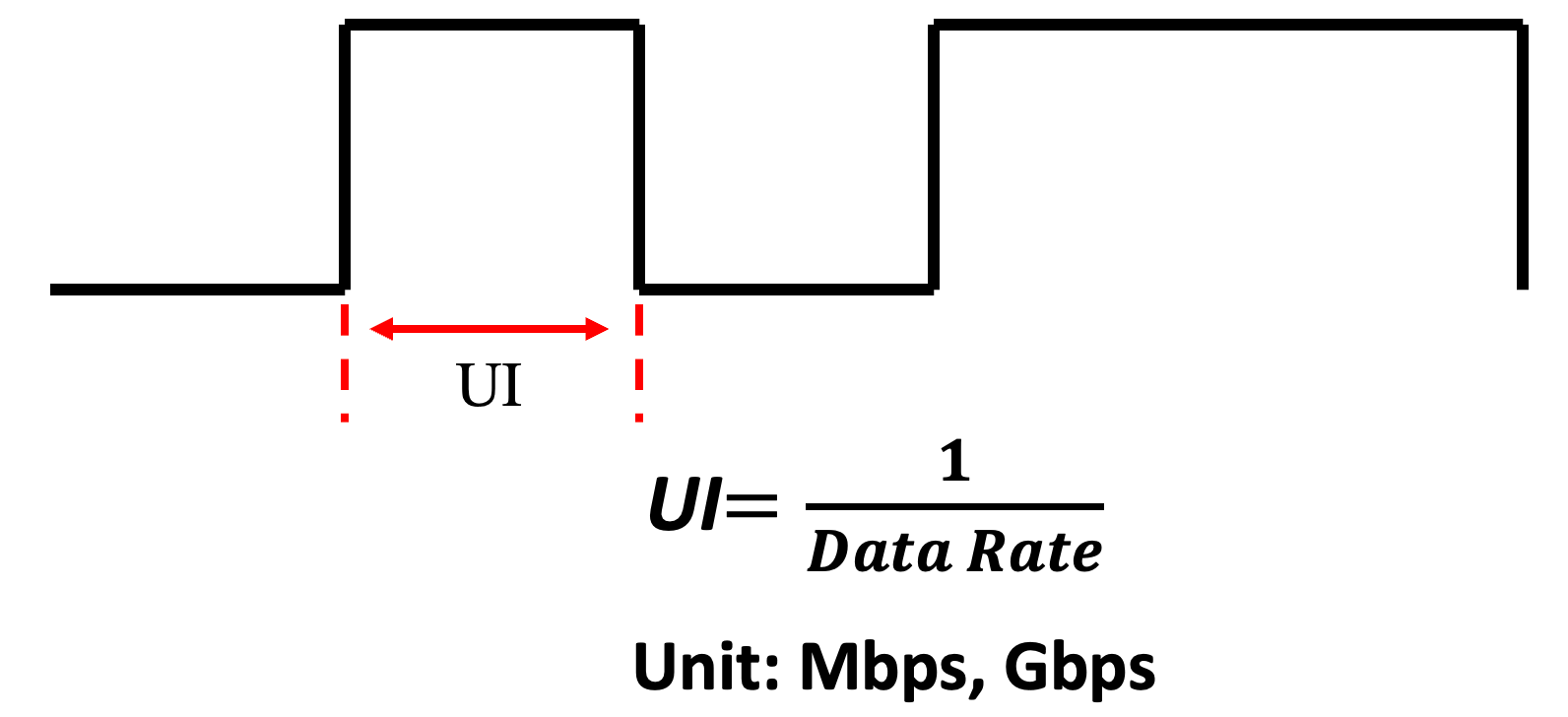

首先,我们来聊聊什么是 UI(Unit Interval)。 它是高速信号设计中最小的时间单位,意思就是:一个「0」或「1」所占据的时间长度,就叫做一个 UI。

这个单位要怎么算呢? 其实很简单,就是把 Data Rate 取倒数。 比如说,如果你设计的是一个 10G的通道,那它的 UI 就是 1 / 10G,也就是 100ps。 也就是说,在 10G 的速度下,每个 bit 的时间长度就是 100ps。 不管这个 bit 是 0 还是 1,都只会占用 100ps 的时间,不会更短了。

而一个UI内的波形不能失真过多,否则Receiver会无法判别此波形是0或1,这就是我们在探讨讯号完整性的初衷。

很多问题都会导致一个UI的波形变差,Loss、Reflection、Crosstalk、Jitter、还有我们今天要强调的“Skew”。 其实每个参数都会对信号质量有所贡献,当Data Rate还没有很高时,绝大多数都是Loss、Reflection、Jitter在搞鬼。 但随着传输速度越来越快,像是现在主流的 112G,甚至是最新的 224G,很多以往「可以忍耐的小问题」都开始变成「致命伤」。 举个例子来说,在224G的速度下,一个UI的长度大约只有8.9ps。 如果你的设计中出现 1ps 的 Skew,那就等于让整个 UI 失真了 11%! 这还只是Skew的贡献,还没加上材料损耗、阻抗不连续、反射等其他破坏因素。 所以呀,Skew这件事情真的很需要被放在心上!

通常会发生Intra-Pair Skew的情况

基本上,只要设计者不恶搞,例如故意把线长不等长,故意乱拉走线的话,Intra-Pair skew通常会发生在以下这些情况:

- Trace Length Mismatch(发生机率低)

- PCB玻璃纤维效应(Fiber Weave)

- Cable

Trace Length Mismatch

我们最前面提到,差动对我们会在Layout上让两条线尽可能等长,拜现在Layout软件进步所赐,56G-PAM4的速度以上,物理长度的Skew已经可以控制在1mil以内。

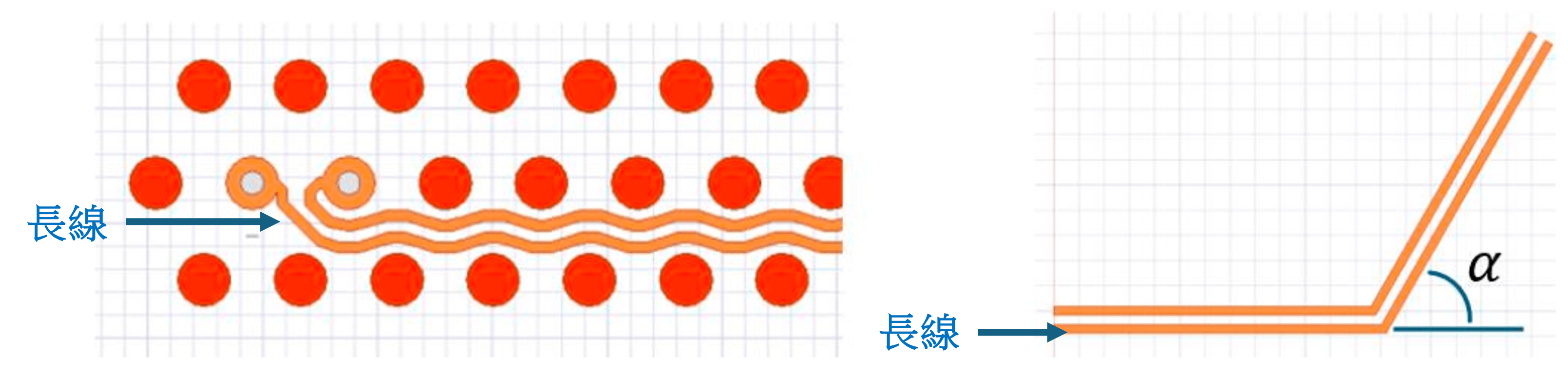

这种线长的不匹配通常来自于转折处,由于外圈会比内圈走得还远,所以内圈的走线就得额外拉长,以匹配线长。

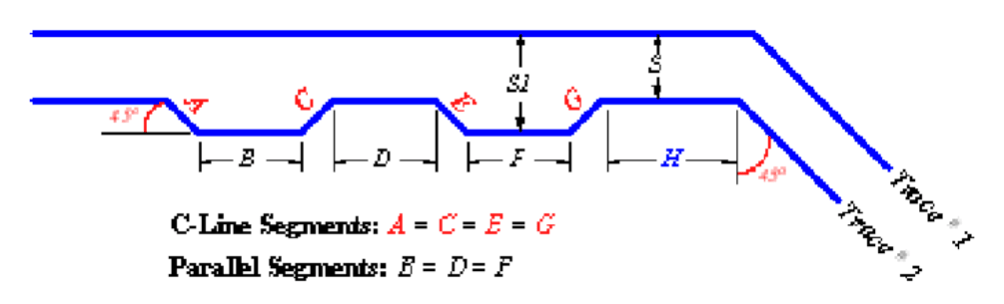

相信业界最有名的莫过于Intel在用的3W2S rule,也就是在差动对去做等长设计时,短的那条线进行绕线补偿时,补偿的高度和宽度的定义,3W指的是两个凸包的距离为3倍的线宽W(B=D=F=3W),2S是指凸包最远的位置与另外一条线距离为2倍的差动对间距S(S1=2S)。

我们在SI这条路上已经遇到太多人跟我们说,要照Intel这条设计准则走,人家是测试过的,一定要照这条做,不然会有问题。 恩... 讲真的,对于SI而言,我们对这个规则是不太关注的,不是说Intel的这条准则有问题,而是,我们相信一条规则是无法适用到全部的高速讯号设计上。 每个设计有不同的叠构、材料、线长、Data Rate等等,真的可以这么简单用一条准则来设计?

要知道当红炸子鸡,nVIDIA推崇的设计是完全不一样喔,那... 两者冲突,您要选谁?

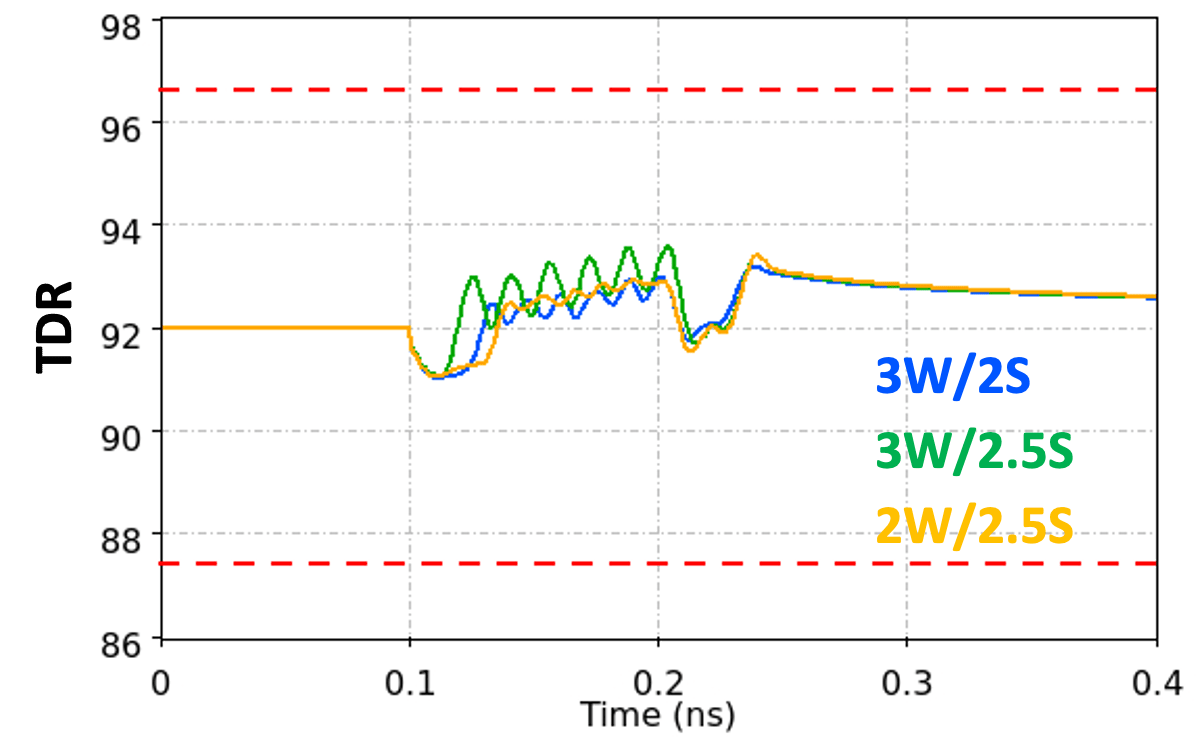

各有门派,我们也不多做讨论,我们的做法是Case by Case,试着透过模拟方法找出最佳的设计,例如这个Case,我们讨论3W2S、3W2.5S、2W2.5S,发现2W2.5S有着较好的阻抗匹配,设计上我们当然选择它!

PCB Fiber Weave

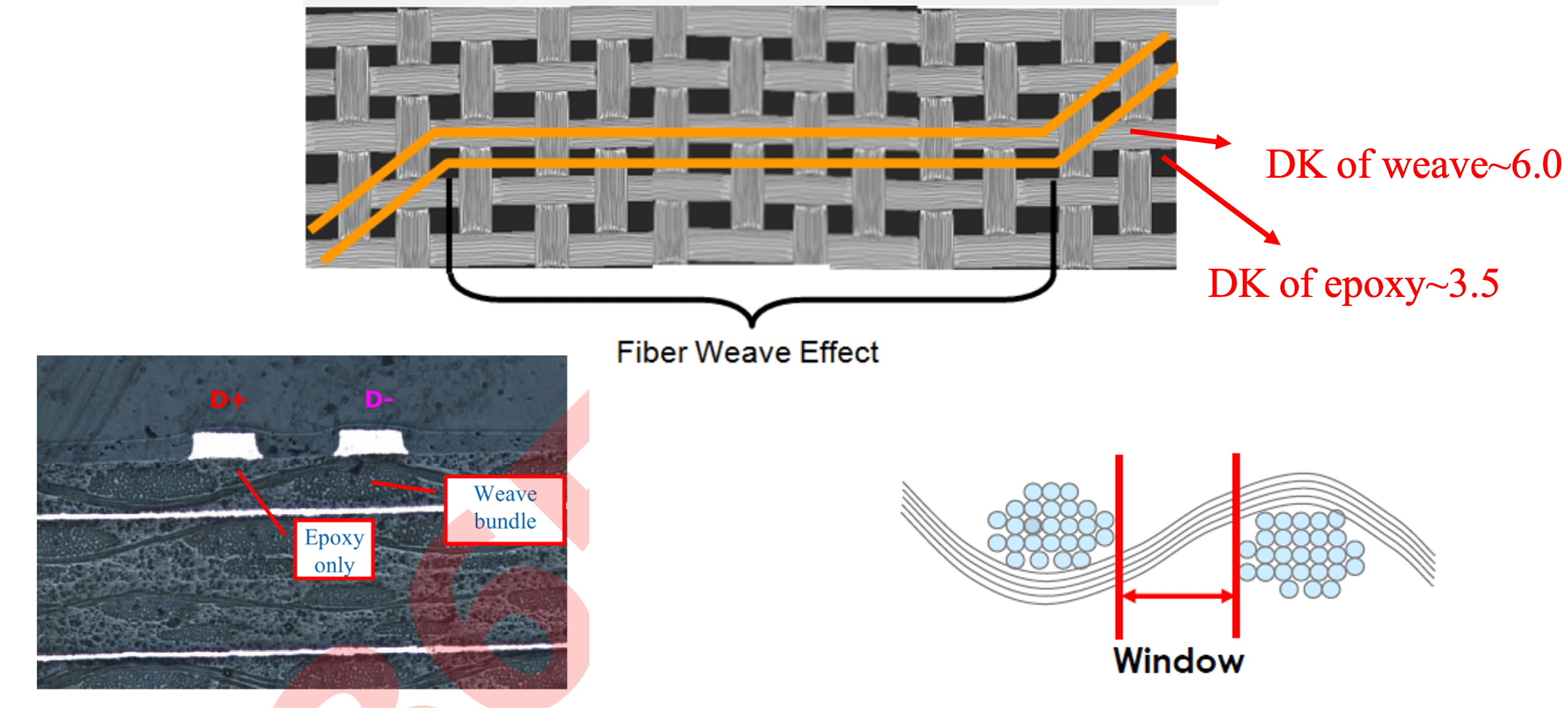

PCB的玻璃纤维效应,这主要来自于CCL材料里头的玻璃纤维与树脂的介电常数(DK)不同所导致。 CCL材料里头的玻璃纤维主要强化材料的刚性,跟织衣服类似,会有经向(Warp)与纬向(Weft)。 像下图,编织成品会留下一个一个洞,这个洞就是树脂的位置。 而传统玻纤(E-Glass)的介电常数大约是6,树脂的介电常数是3.5,两者合起来就接近4.4,这样可以理解为什么传统FR4材料的DK是4.4了吧!

由于材料内的DK有落差,会使得差动对两条线“可能”参考到不同的DK,两条线的讯号传递速率会变得不一样,越大的DK则讯号传递速率会变慢,而导致两条线到Receiver时会有Skew产生。

v=cεr−−√

而且,很讨厌的是,因为Fiber weave产生的Skew,还是随机出现的。 因为,每张板子的每个位子的玻纤是不同的,所以就算是一样的走线,在每批料之间也是不一样的状况,所以文章开头我们才会说,各位有没有遇过随机发生的状况!

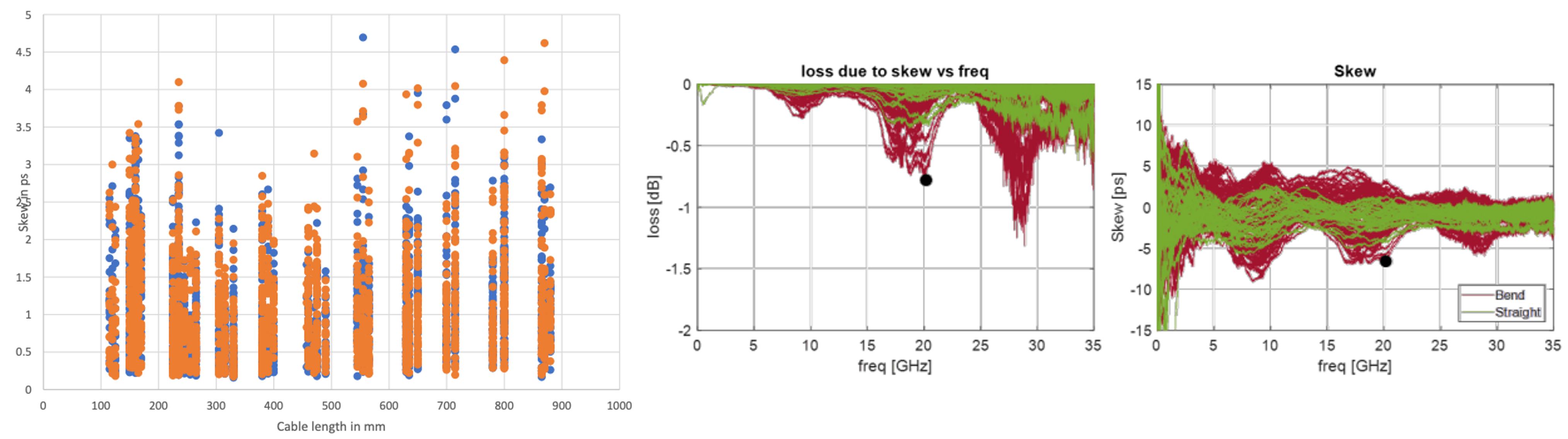

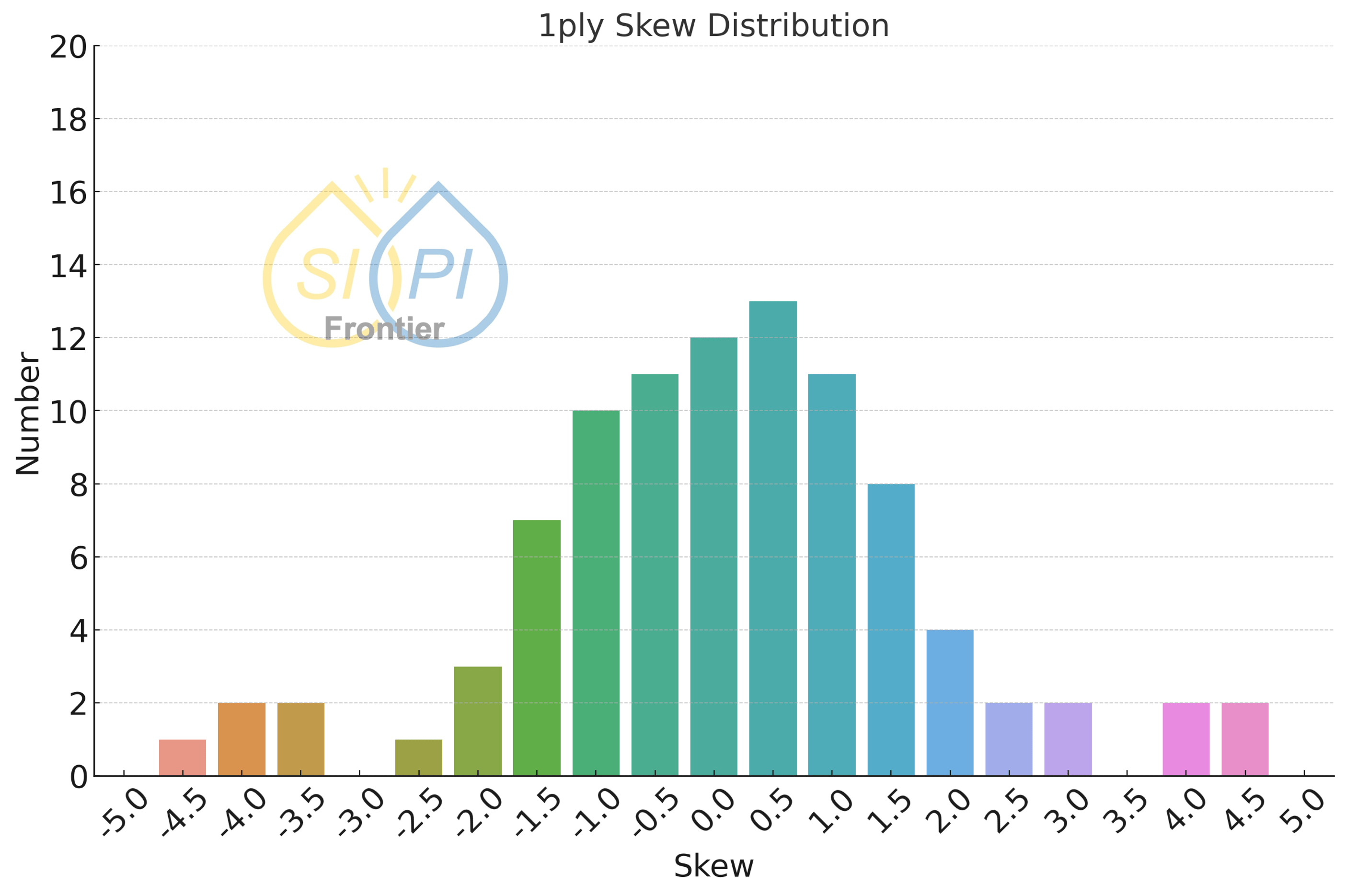

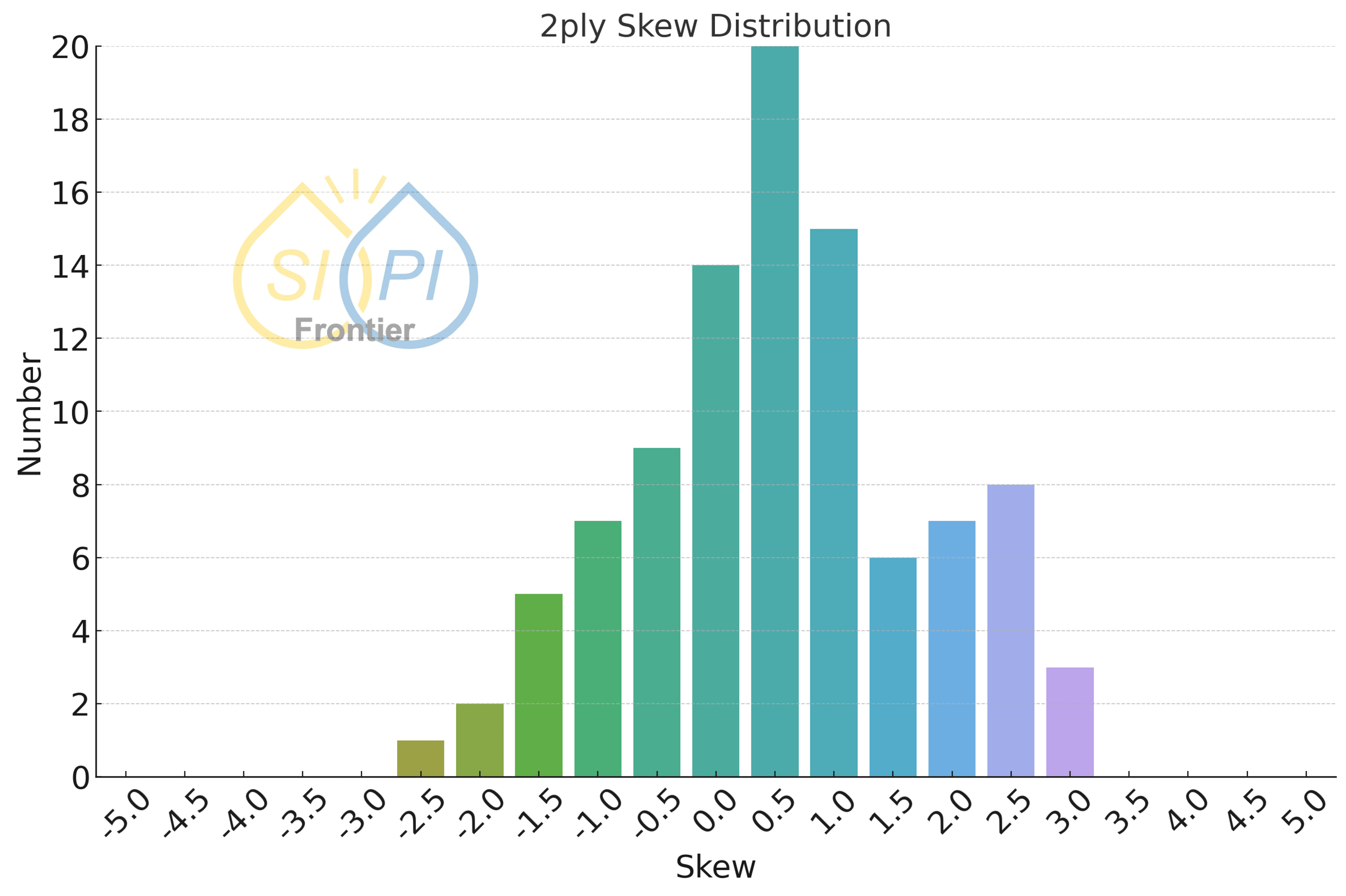

这边我们介绍一个常见的做法,以减少玻璃纤维造成的Skew效应。 透过将CCL叠两层,或称2ply,将树脂的孔洞变小,从数据来看可以很明显看到Skew会更加集中在较小的范围,不像1ply那样,会有一些离散数据落在较大的skew值。

Cable

我们在这边介绍过Cable已经成为现在机台内部连接一个重要的关键零组件,nVIDIA的GB200 NVL36/72都用了Flyover cable以减少PCB走线带来的损耗。

对于损耗控制上,Cable的确有着非常好的特性,可是在制造上,由于传统的Twinax cable除了两根讯号线外,还会再塞入GND pin,这个GND pin可以用来抑制EMI。 可是由于制造的tolerance,当这根GND pin位置偏掉,靠得离某根讯号线太近,则会引起PN unbalance,skew就会出现,common-mode noise也随之发生。 (有兴趣可以参考这里)

再加上,Cable绝对是需要弯折的,在弯折的时候,两条线的电磁场可能就没办法保持恒定,进而导致Skew的产生!

所以在高速信号SI分析上,我们就得分析不同的skew差异对于通道的影响是什么,尝试找出Worst-case,以满足大量量产的系统可靠度! 说实在话,真的是件大工程!