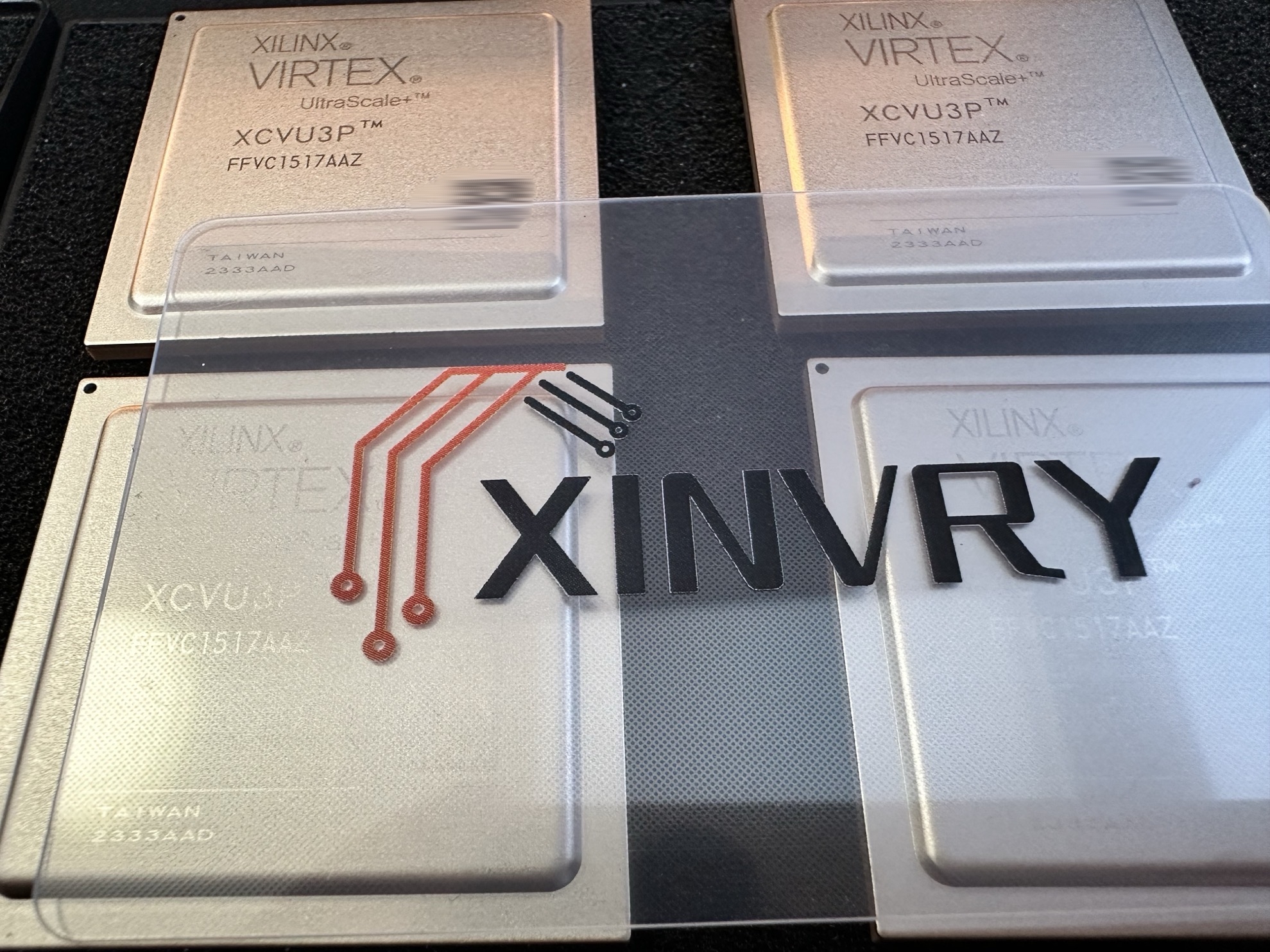

XCVU3P‑2FFVC1517I AMD Xilinx Virtex UltraScale+ 系列中的高端 FPGA,基于 TSMC 16 nm FinFET+ 工艺及第三代 3D IC 堆栈互连技术(SSI),旨在为数据中心互连、高性能计算、网络加速和信号处理等苛刻应用提供领先的性能‑功耗比。该器件在中端 FPGA 中拥有超大逻辑容量、丰富的片上存储及业界顶尖的串行 I/O 带宽,是追求极致带宽与算力的设计首选。

XCVU3P‑2FFVC1517I 采用 TSMC 16 nm FinFET+ 工艺,结合 AMD 第三代堆栈硅互连(SSI)技术,实现多晶 Die 的低感抗互连,打破摩尔定律限制。该架构在保持极高逻辑密度的同时,提供行业领先的信号处理带宽和串行 I/O 性能,并通过先进的电源管理选项,在满足系统性能需求的前提下,实现功耗与热耗的最佳平衡.

逻辑资源

逻辑单元(LE):862 050 个,可组成 49 260 个 LAB/CLB,每个 CLB 包含 8 个 6 输入 LUT 和 16 个触发器。

可编程布线:超大规模互连网络,支持高效自动布局布线和多时钟域设计。

存储资源

总片上 RAM:118 067 200 位(≈ 118 Mb),包括 Block RAM 与 UltraRAM。

Block RAM:308 块 18 Kb M18K,支持真双端口、简单双端口和 FIFO 模式;

UltraRAM:288 Kb 高密度存储单元,可级联形成更大容量阵列,适用于替代外部 SRAM 的大规模缓存需求。

DSP 资源

DSP48E1 切片:1 368 个,每个切片集成 25×18 乘法器、预加器及 48 位累加器,峰值乘加性能可达数万亿次/秒,满足滤波、FFT 和机器学习推理等高吞吐量计算任务。

时钟管理

混合时钟管理单元(CMT):10 个 CMT 单元,每个集成 MMCM 和 PLL,支持时钟倍频、分频、相位对齐及抖动清除;

全局时钟网络:多条低偏斜时钟线,确保多时钟域设计的时序闭合和高性能运行。

高速串行收发器与 I/O

串行收发器:40 条通道(32× GTH @16.3 Gb/s + 8× GTY @32.75 Gb/s),支持 PCIe® Gen3/4、100 GbE、CPRI、Aurora、DisplayPort™ 等协议;

用户 I/O:520 条可编程引脚,支持 LVTTL、LVCMOS(1.2–3.3 V)、SSTL‑2/‑3、HSTL 等标准,采用 SelectIO™ 技术可混合部署;

总 I/O 带宽:数 Tb/s 级别,满足大规模数据交换和外设互联需求。

电源与热特性

核心电压(VCCINT):0.825 V–0.876 V;I/O 电压(VCCO):1.2 V–3.3 V;

工作温度:–40 ℃ 至 +100 ℃(结温);

功耗管理:多电源域设计,支持动态功耗控制与深度睡眠模式;16 nm FinFET+ 工艺带来极低的静态与动态功耗;

热设计:1517‑ball FCBGA 封装(40 × 40 mm,1.0 mm 球间距),低热阻,适合风冷或散热片方案。

封装与配置

封装形式:1517‑ball FCBGA(40 × 40 mm,1.0 mm 球间距);

配置模式:支持 Master/Slave SPI、SelectMAP 并行(x8/16/32)、JTAG 和 MultiBoot;

安全特性:AES‑256 位流加密、CRC 校验和 eFUSE 锁定,确保 IP 保护与安全启动。

等级考试试卷(五级)真题)