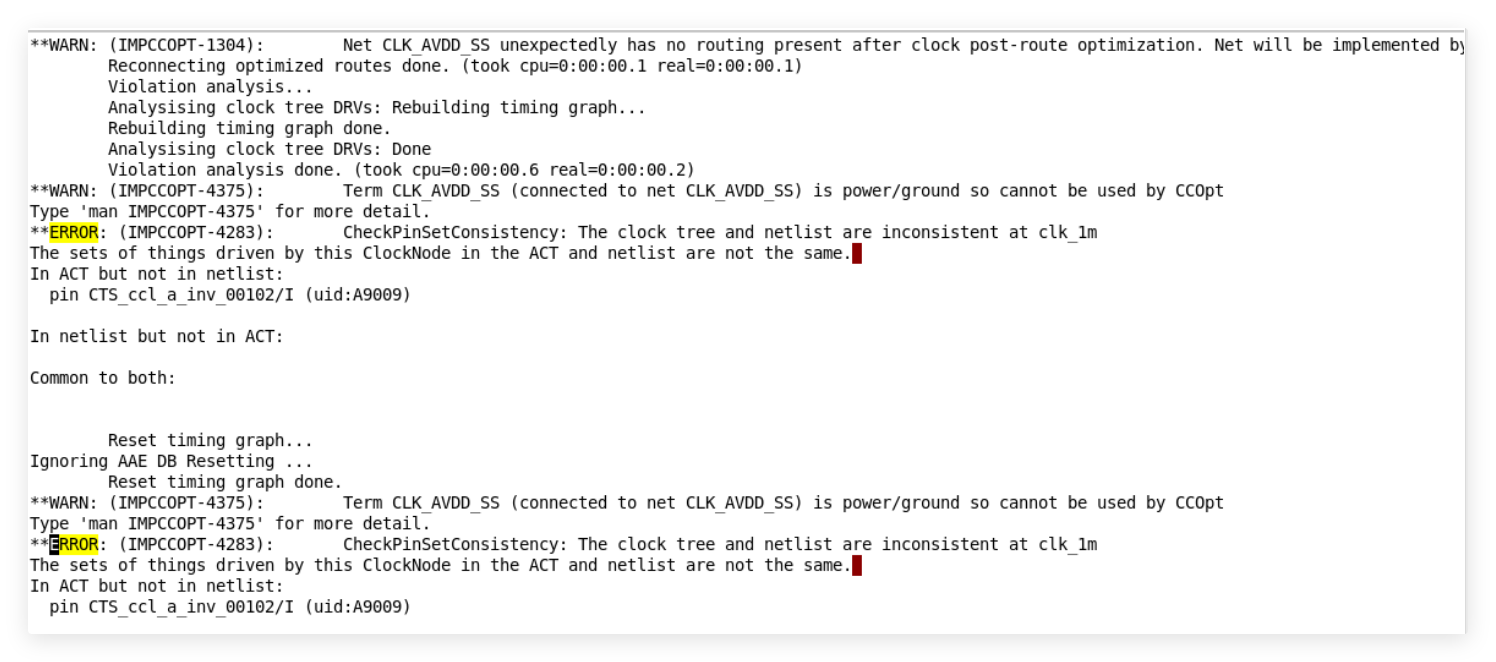

今天上午有学员在做公司自己项目CTS时发现跑不下去,报了如下所示的错误IMPCCOPT-4375。

复杂时钟设计时钟树综合(clock tree synthesis)常见20个典型案例

第一次遇到这种错误,其实可以从提示信息上入手。

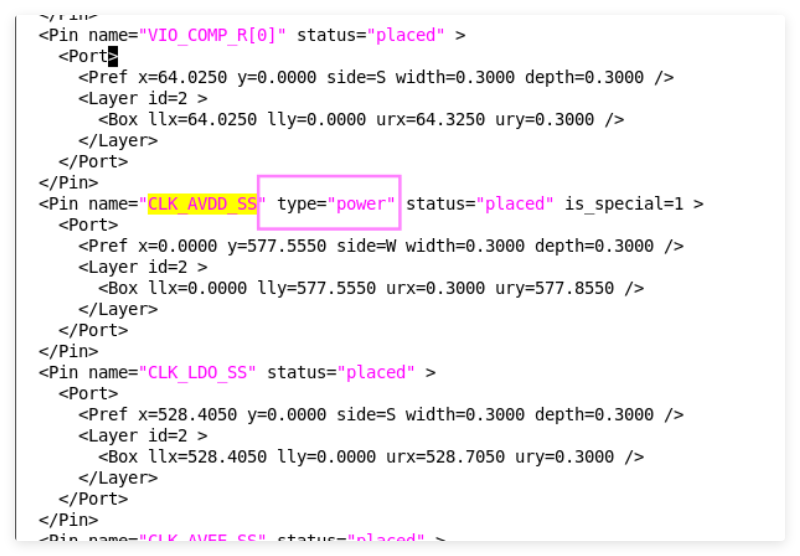

Term CLK_AVDD_SS is power /ground (这个信息非常重要)!

也就是说ccopt engine发现这个port是接到电源地的,但是你又要让它做clock tree,这不是明显为难它吗?

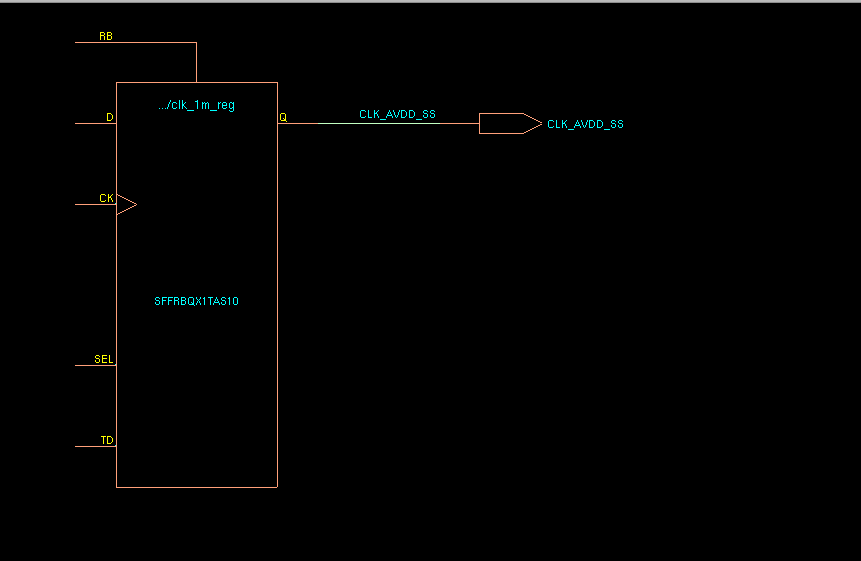

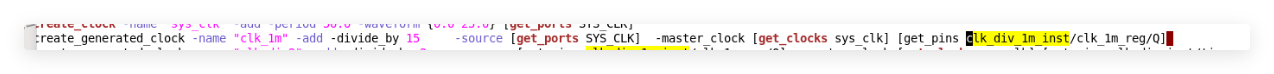

所以我们选中一个io port,看看它的逻辑连接。trace连接关系后如下图所示,clk_1m_reg的输出直接送到这个io clock port。

稍微有经验的后端工程师,应该可以判断出这个寄存器必须定义generated clock,否则这里就一定会漏clock tree。

数字SoC芯片复杂时钟结构设计时钟树综合典型案例(最复杂的时钟案例也不过如此!)

从逻辑关系上看,这里的确没啥毛病。

这时候就剩一种可能性了——io port的属性问题了!

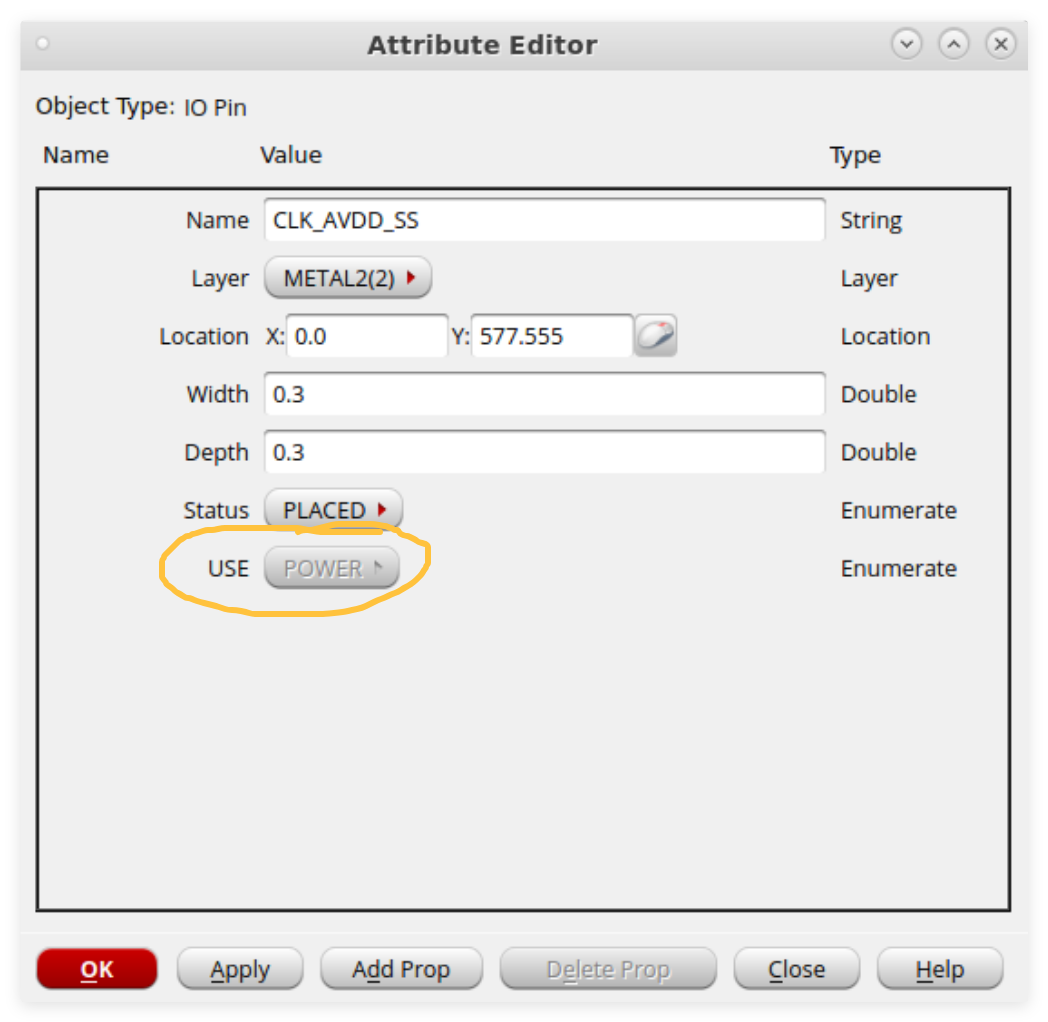

选中这个io port,右键查看它的属性,我们马上就可以看到这个port有Power属性!

到这里我们就找到问题了。只需要把这个io port的USE类型改成普通信号类型即可。

更改后重新跑下CTS就可以正常做完时钟树综合。

这种问题一般是出现在数模混合芯片中,而且子模块的io port摆放信息是通过读入模拟工程师提供的def文件。

最后分享一个非常经典的时钟树综合CTS(clock tree synthesis)跑不出来的典型case。

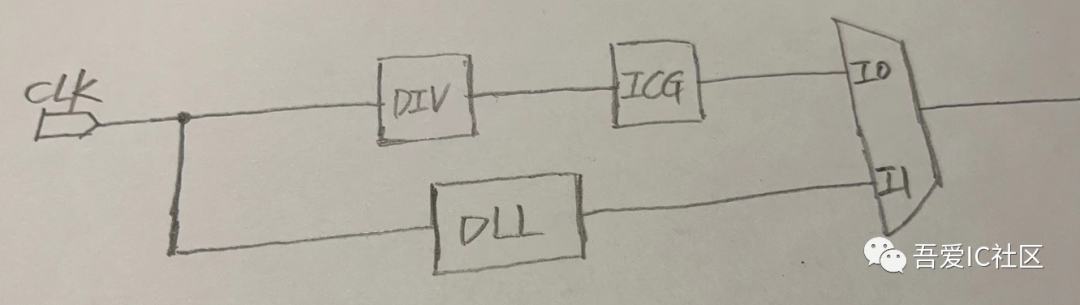

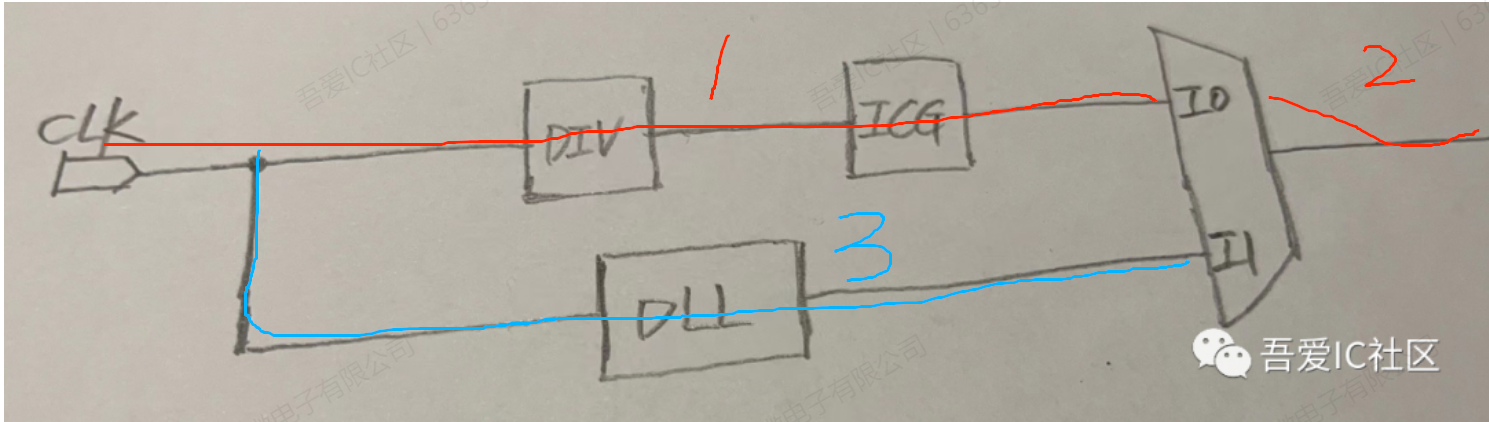

在有些设计中会通过DLL Macro来调整时钟的相位,比如90度,180度。下图中的Mux的I0端接原始时钟CLK,I1端接经过DLL调整相位后的时钟。而且DLL内部其实就是一段clock tree,它内部的delay值为2ns。

遇到这样的设计,如果你仅仅是个跑PR Flow的工程师,那么这个时钟树综合出来的结果一定惨不忍睹,而且通常是跑不出来的。如果你不希望未来被工具所替代,一定不能仅仅会跑后端流程。

因为Mux后带的sink。都是挂在CLK这个时钟下,默认情况工具会把Mux的I0和I1两路做clock balance。因此,工具做时钟树综合的clock balance阶段会在I0端垫个约2ns的clock inverter chain。

【解决方案】

我们可以在做时钟树综合时在Mux的输出端定义一个create_clock,并且把Mux的I0和I1 pin设置成ignore pin。这个方法其本质也是用了“分段做tree”的思想。工作做tree会分别作出下面三段tree出来,而且第一段和第三段是完全没有关系的。

还有一种解决方法是通过设置set_clock_sense -stop_propgation $mux_I1_pin。原理是类似的。这个方法就是让CLK时钟属性不要穿过Mux。

等级考试试卷-理论综合)

)

![[第十六届蓝桥杯 JavaB 组] 真题 + 经验分享](http://pic.xiahunao.cn/nshx/[第十六届蓝桥杯 JavaB 组] 真题 + 经验分享)