写在前面:

今天遇到一个问题,就是跑好的工程需要修改一下一个管脚的电平标准。想着这么简单调整,不至于要重新在对Vivado工程进行综合实现一次,太浪费时间了。请教了师兄,师兄告诉我说,可以直接在dcp文件中修改,然后生成bit。经过我一下午的摸索,现将整个摸索的结果展现如下,在此感谢我的张师兄!

正文:

此处以工程FPGA_FIR32P_V2.0_20241023为例,该工程已经综合实现完毕,发现时钟管脚的电平与现实不符,需要进行调整。此时将\FPGA_FIR32.runs\impl_1文件夹下的FIR32_TOP_routed.dcp单独复制到新的路径下。

图 1 将dcp文件拷贝至新路径下

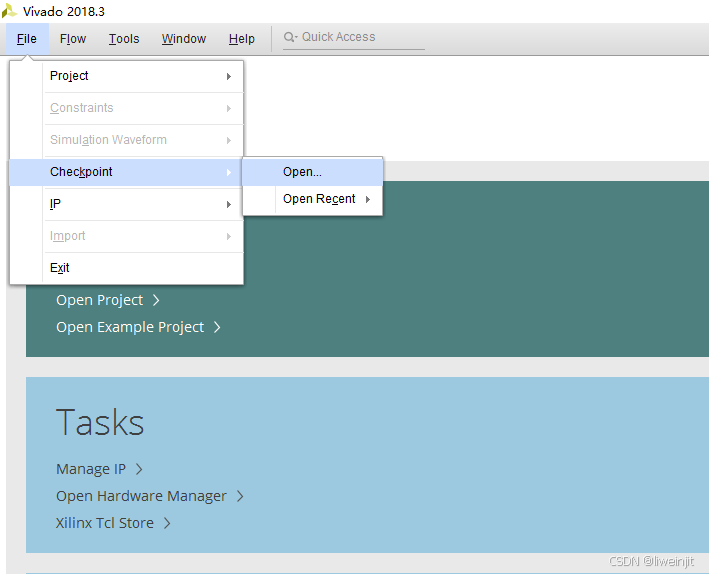

并使用Vivado打开该DCP文件;

图 2 在Vivado中打开dcp文件

图 3 选中dcp文件

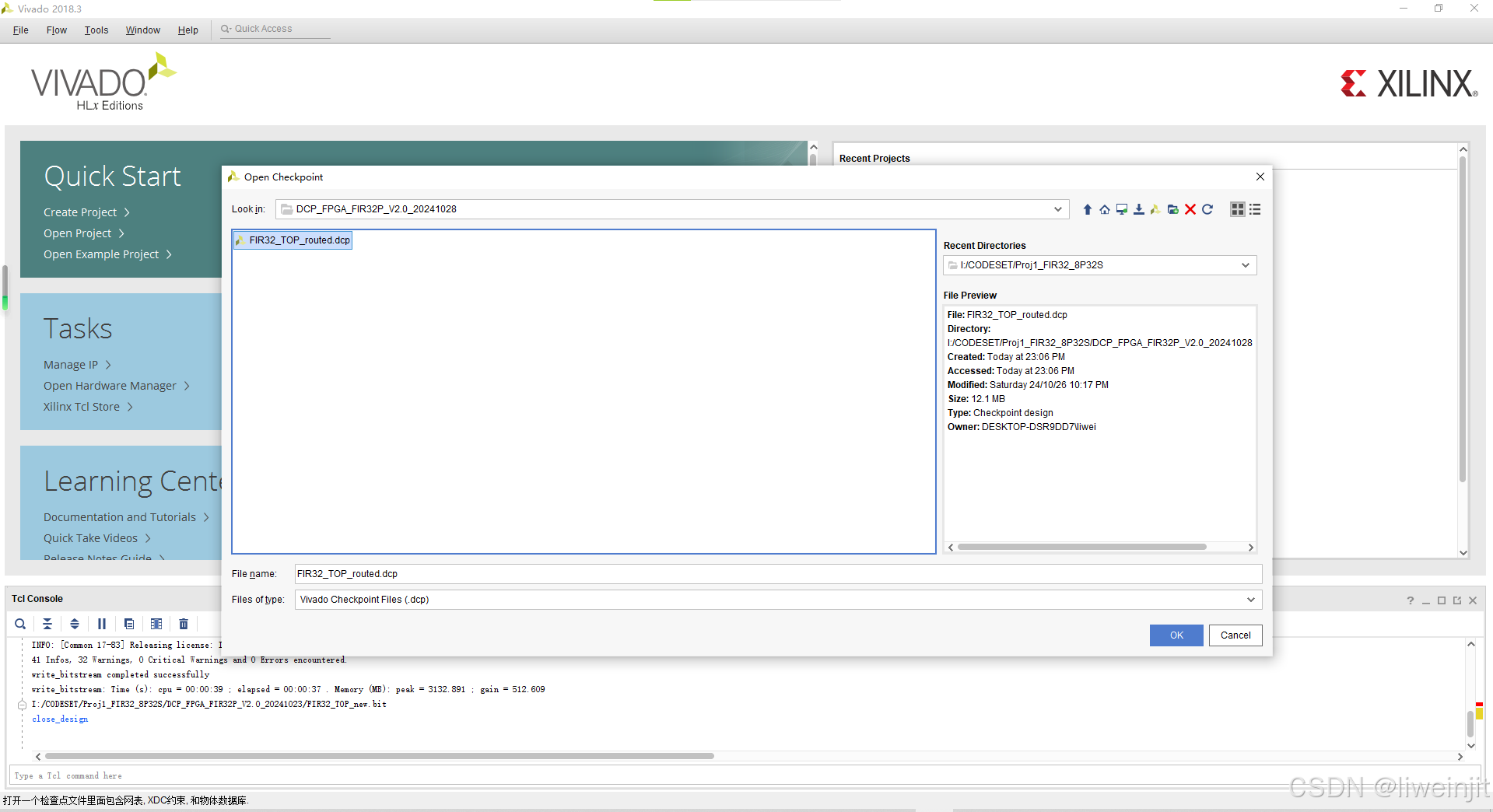

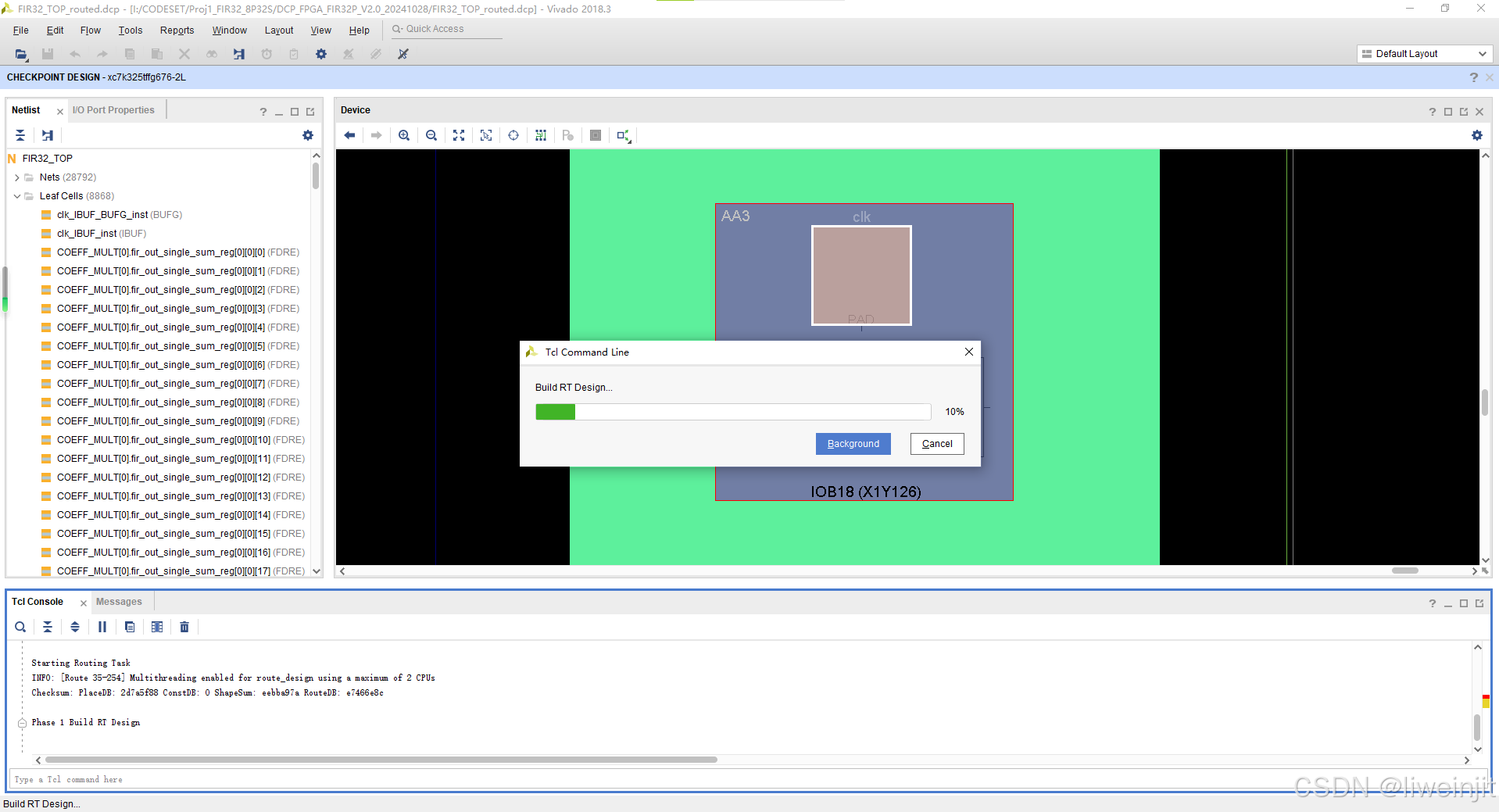

打开DCP文件后,在Netlist中选中所需要修改的模块,本例中为clk_IBUF_inst(IBUF),此时在Device中会看到一个亮点,即该模块在芯片上的位置

图 4 选中所需要修改的cell

将这个亮点进行放大,就可以锁定clk_IBUF_inst(IBUF)在device上对应的管脚

图 5 选中该cell在Device中对应的器件模块

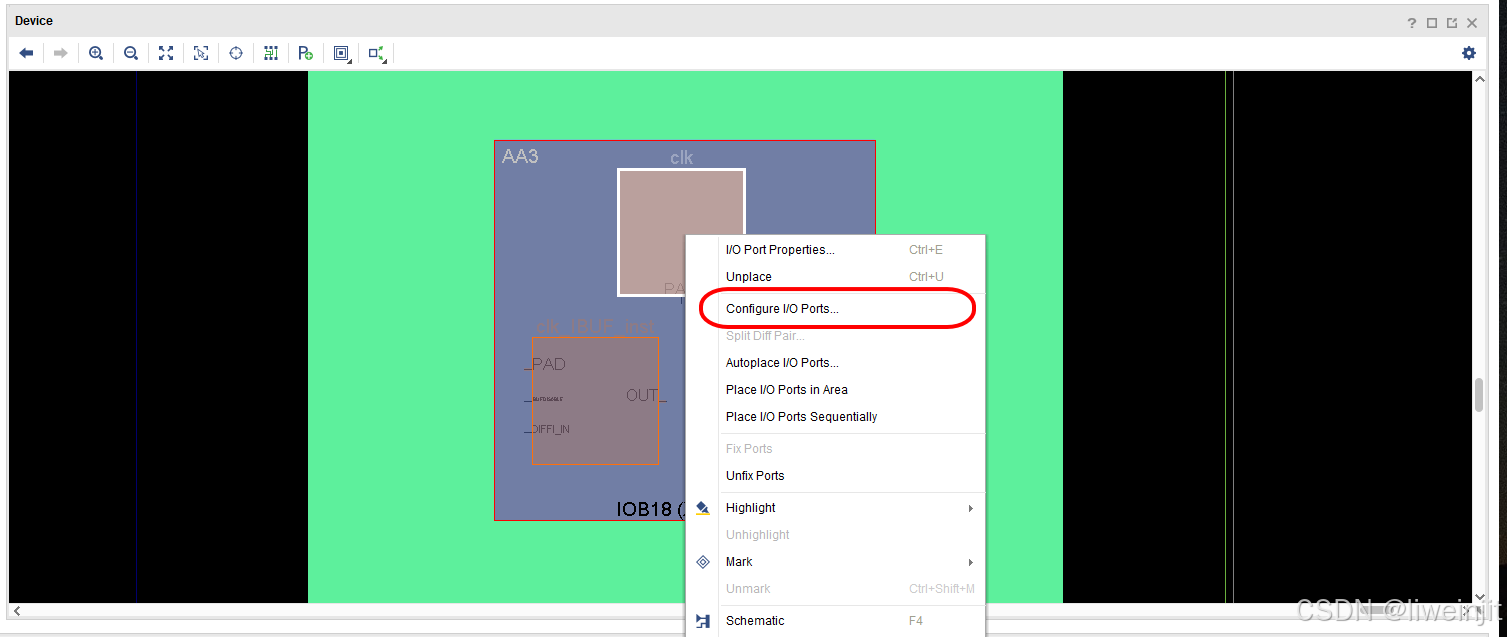

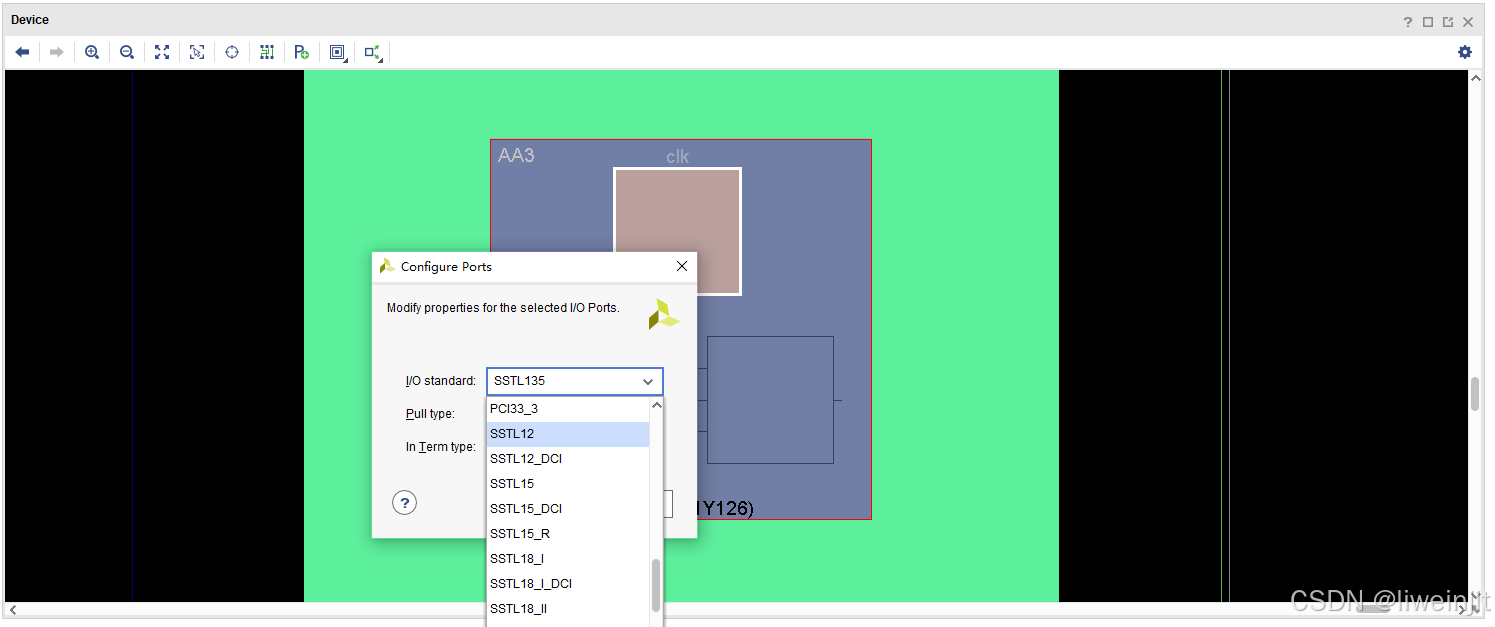

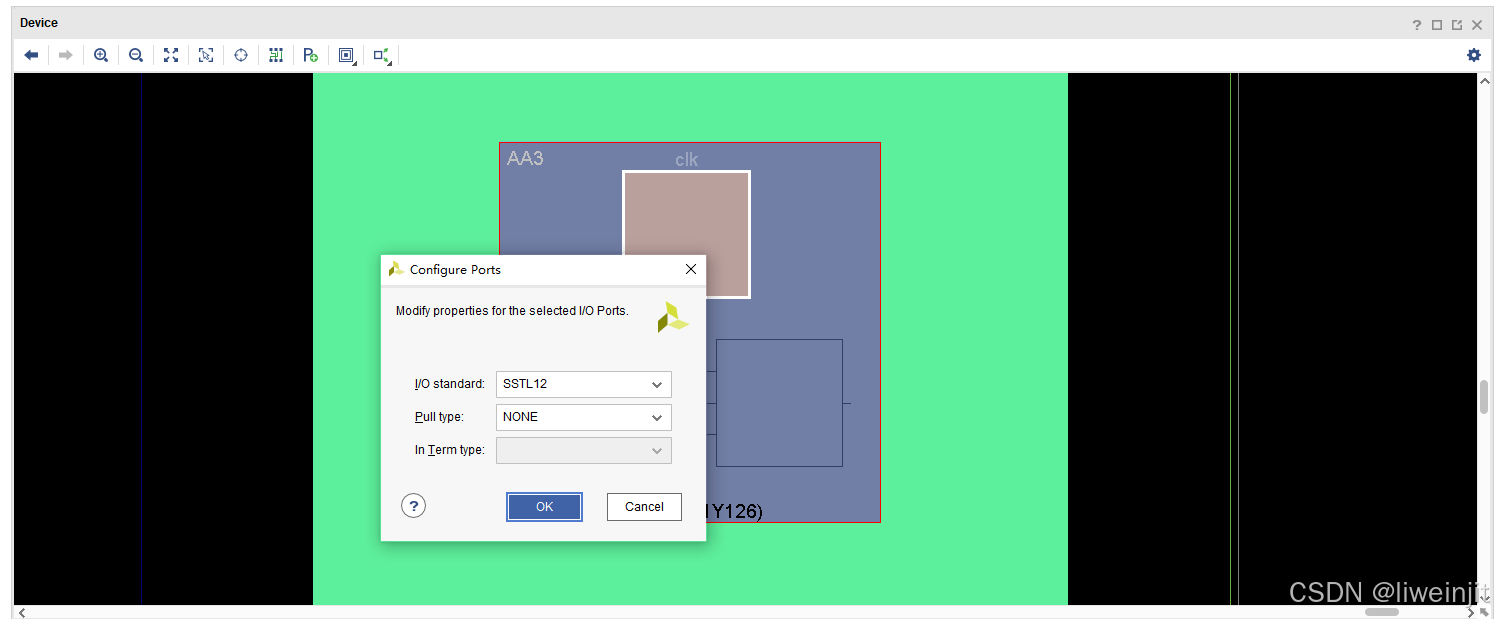

将鼠标放置到clk_Pin上,右击选中“Configure I/O Ports”,然后开始修改时钟电平,将原先的电平SSTL135调整为SSTL12,PullType选择默认,点击“OK”按键。至此,该管脚的电平已经在Device进行了修改,然后需要将修改后的DCP文件进行保存。

图 6 选中“Configure I/O Ports”

图 7 修改时钟电平参数

图 8 确认修改参数完毕

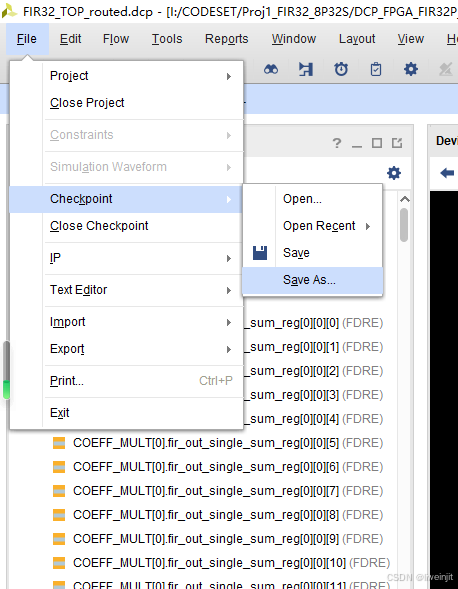

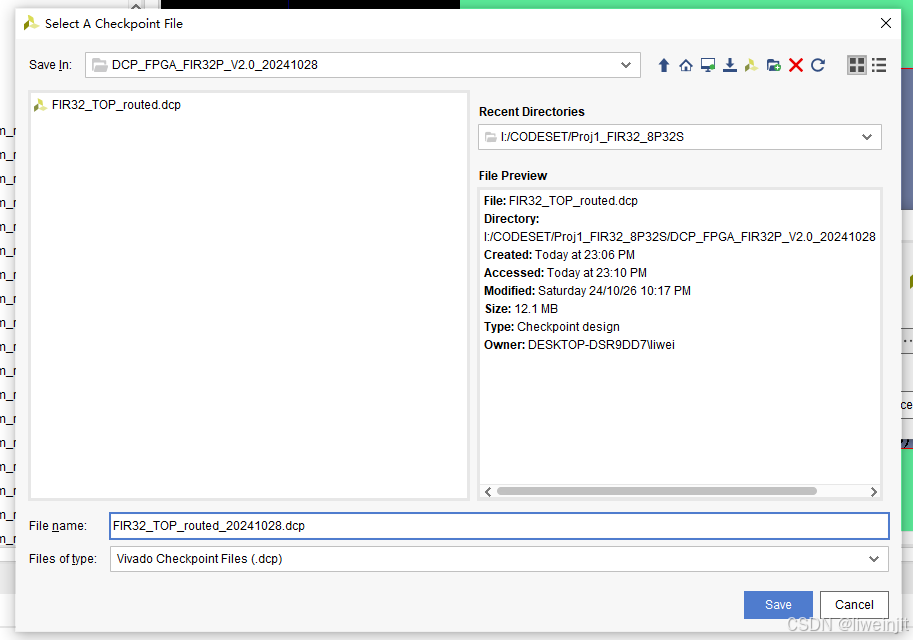

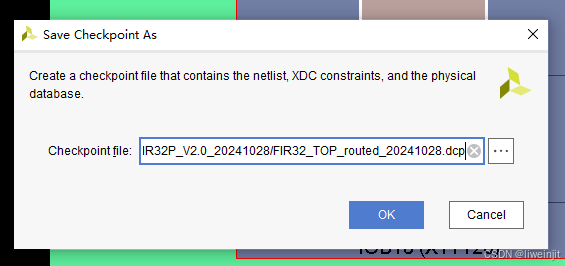

点击Vivado软件左上角的File,选中CheckPoints->Save As,将修改的DCP文件重命名保存。

图 9 保存修改后的DCP文件-1

图 10 保存修改后的DCP文件-2

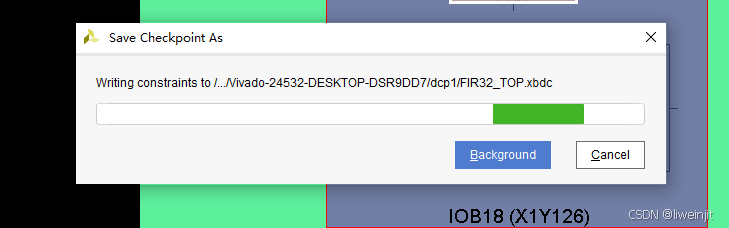

图 11 保存修改后的DCP文件-3

图 12 保存修改后的DCP文件-4

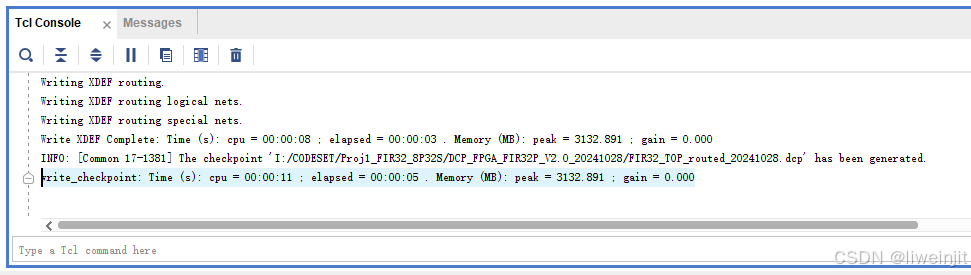

待Tcl Console中显示 The checkpoint XXXX has been generated后,说明该新的DCP文件已经保存成功。

图 13 DCP文件保存成功

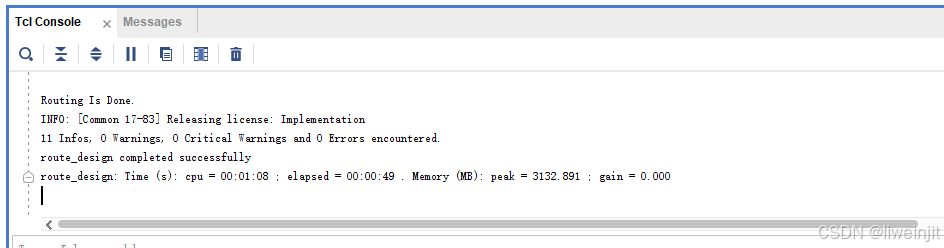

开始重新进行route,在Tcl Console中敲入命令 route_design,等待系统重新布线完成。

图 14 对新修改的DCP文件重新route

图 15 route_design成功

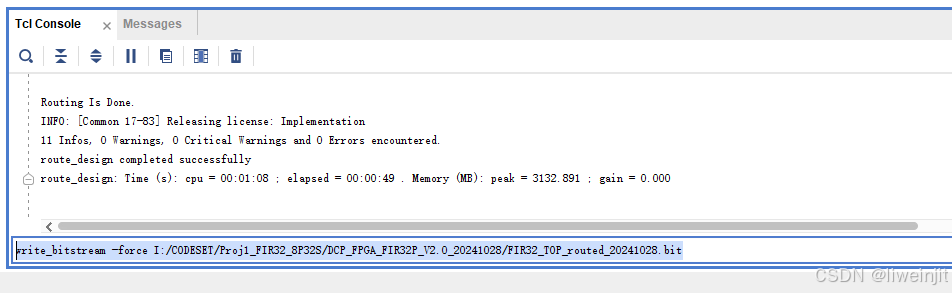

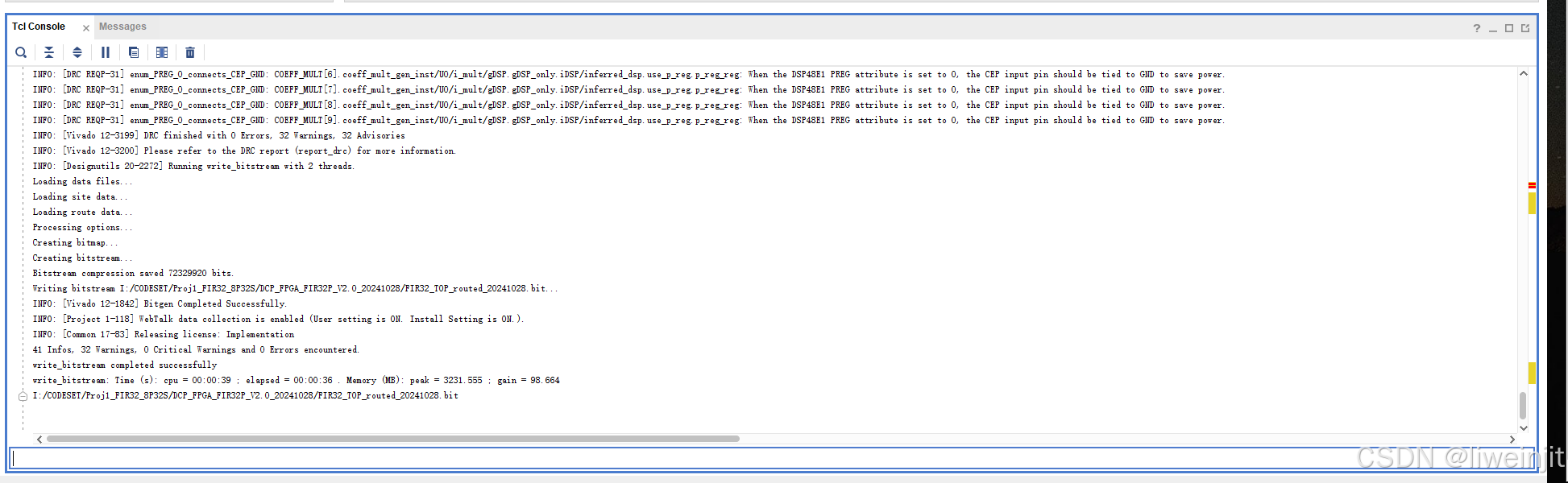

布线完成后需要重新生成bit,在Tcl Console中敲入命令

write_bitstream -force [Path]/FIR32_TOP_routed_20241028.bit,

等待Tcl Console中提示 write_bitstream completely sunccessfully,至此新的bit生成完毕。

图 16 route后开始进行write_bitstream

图 17 write_bitstream成功

图 18 新生成的bit文件

可以将新的bit替换原先的bit文件。

总结:

1.整体的思路就是

- 修改并保存 “XXX_routed.dcp”文件

- 重新route_design

- 重新write_bitstream

2.拓展开来,我们在学习使用Vivado时,最好能够了解整个开发的每一步,而且对Non-Project模式也需要了解一下,将Project模式与Non-Project模式相结合,从而进行高效开发。

.cdr)