SIwave 是一种电源完整性和信号完整性工具。CrosstalkScan 是 SIwave 中最重要的工具之一,也是本博客的主题。

Zoscan 在另一个博客和视频中进行了解释。Zoscan 突出显示跟踪中的缺陷。它计算沿路径的阻抗。此外,在另一篇博客和视频中,还讨论了 TDRwizard,TDRwizard 的主要工作是识别所有走线中转换的不连续性或任何缺陷。串扰扫描器的主要工作是识别走线周围接地的任何故障,包括过孔。它突出显示了痕迹没有得到很好的隔离和保护的区域。

图 1:Zoscan 求解器 4th图标从左侧开始

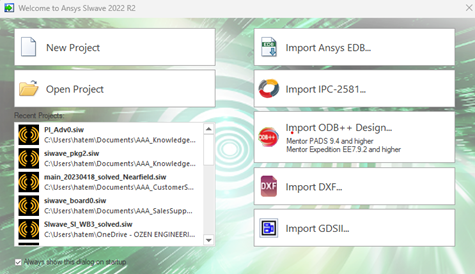

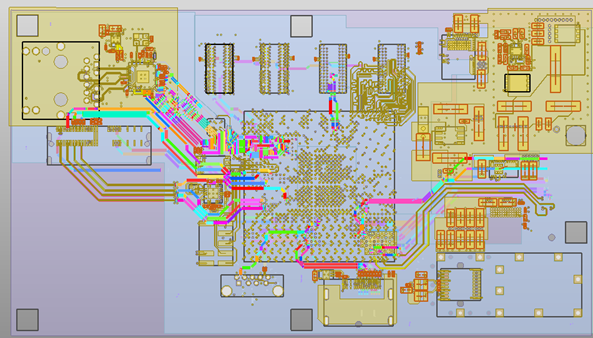

SIwave 不应用于构建 PCB。虽然这是可能的,但这不是使用 SIwave 的最佳方式。SIwave 可以导入以下类型的 CAD 文件:

图 2:SIwave 中的“导入”对话框

SIwave 从 CAD 文件中提取大量信息,例如叠层、材料、组件和网络。因此,模型已准备好进行求解。

- Crosstalk Solver – 频域。

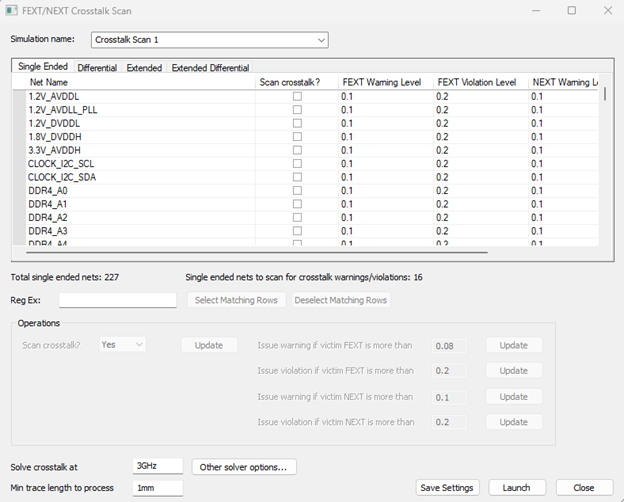

单击 Crosstalk Scan 求解器并选择频域选项。

SIwave: DC、PI、SI 或辐射中的任何过程都从选择求解器开始。选择求解器后,SIwave 会生成一个看起来像表单的对话框。用户需要检查表单并填写缺失的信息。

例如,SIwave 使用模型中的所有现有跟踪填充对话框。可以选择一些行或解决所有行。SIwave 使用先进的技术,可以非常快速地解决所有线路。

图 3:串扰 – 频域对话框

请注意,此处 SIwave 仅选择跟踪。任何被归类为功率平面 SIwave 的东西都不会将其放入表格中。

现在,在表中,有四个跟踪类别:Single、differential、extended 和 extended differential。请务必检查所有内容。对于每个跟踪,需要指定限制、警告和违规限制。这些数字有助于稍后放大不良和最差的区域。

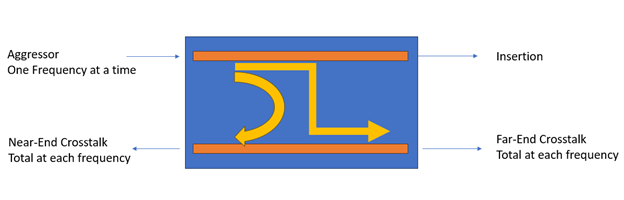

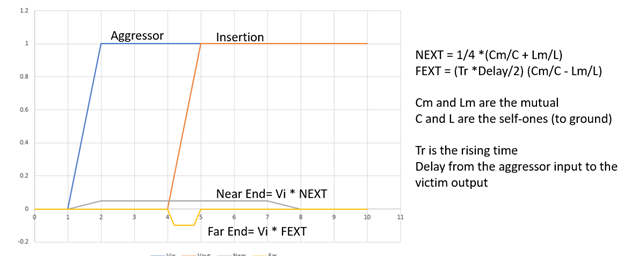

那么什么是 FEXT?什么是 NEXT?SYZ 求解器提供当正弦信号注入干扰源迹线时从其他迹线的端口看到的总串扰。串扰有两种类型:远端串扰和近端串扰。远端始终与波传播的方向相同。来自不同部分的串扰同时到达受害者的远端端口。而在近端串扰中,波必须反转其方向。来自不同部分的串扰不会同时到达受害者的近端端口。

图 4:近端和远端串扰

在串扰扫描求解器中,假设信号是阶跃响应,而不是正弦信号,即任何数字通信中的传统信号。然后,观察受害者端口的信号。在远端和近端看到的信号是众所周知的,但它们的幅度却不是。对于远端,它是 FEXT 乘以 Vi,对于近端,它是 NEXT 乘以 Vi。FEXT 和 NEXT 与互电容和互感有关,公式如下所示。

图 5:FEXT 和 NEXT 定义

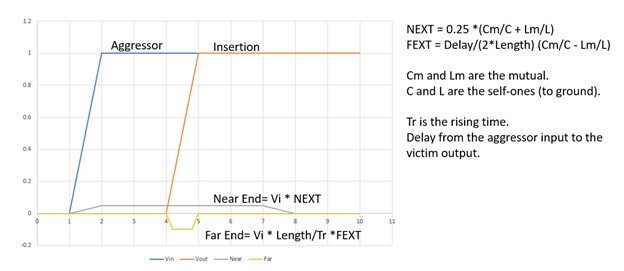

在 SIwave 中,FEXT 的定义方式略有不同:

图 6:SIwave 中的 FEXT 和 NEXT 定义

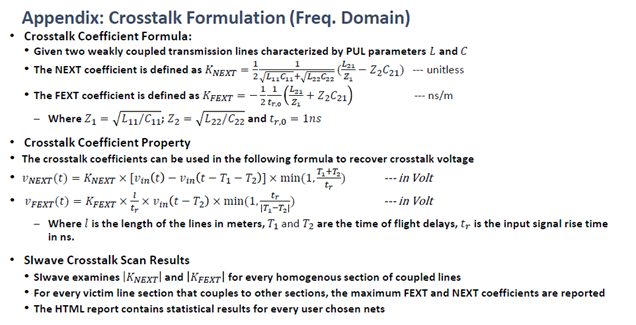

如果您对简化不满意,这是更详细的公式:

图 7:SIwave 中的 FEXT 和 NEXT 定义详解

回到设置:

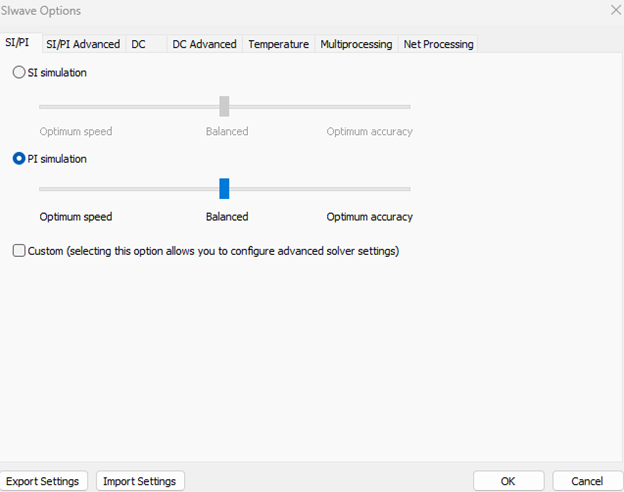

使用 “Other solver options” 按钮来决定解的精度。三个选项:最佳速度、平衡或最佳精度。从平衡开始,在一个解决方案之后,人们可以决定如何为下一个解决方案做什么。

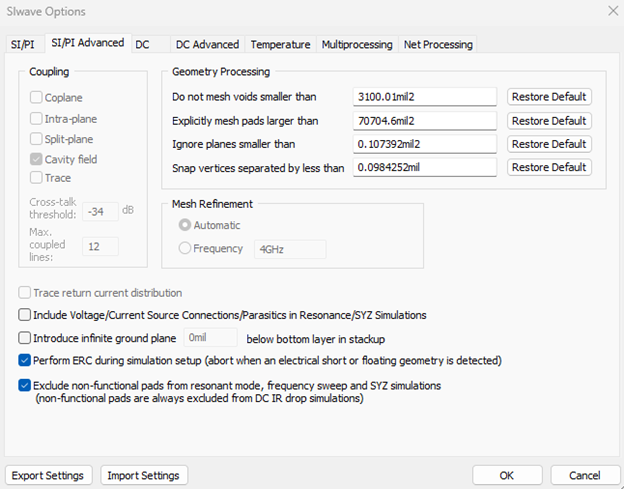

图 8:高级选项 SI/PI 选项卡

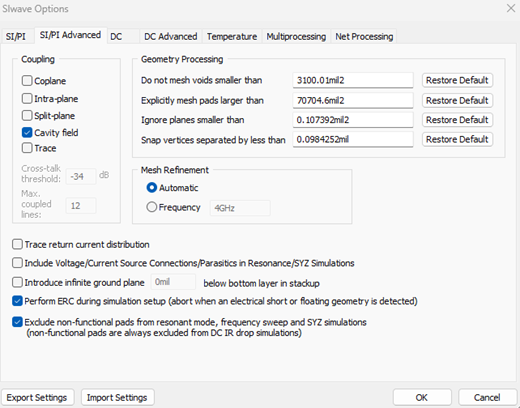

SI/PI Advanced 中还有更多高级选项:

图 9:高级选项 SI/PI 高级选项卡

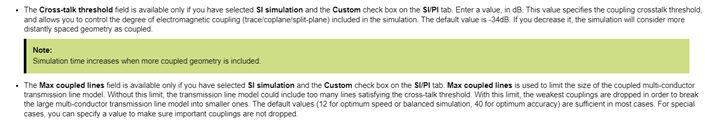

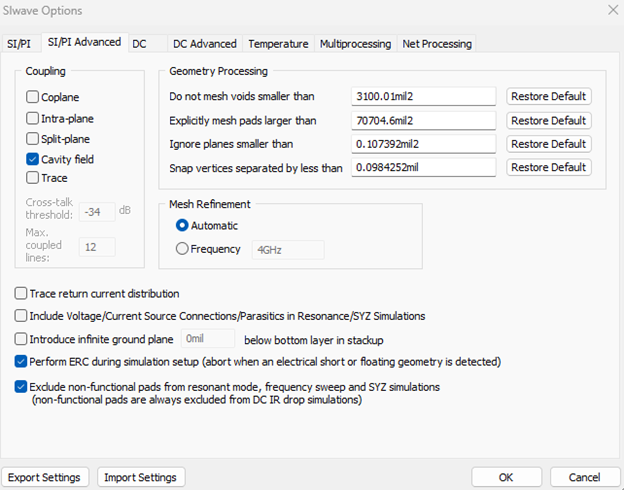

如果激活了 Custom 按钮,则用户在 SI/PI Advanced 选项卡中有更多选项。

图 10:串扰阈值定义

图 11:高级选项 具有更多选项的“高级 SI/PI”选项卡

可以控制网格划分并强制求解器以特定频率进行串扰扫描的网格划分。用户还可以更改串扰阈值和最大耦合线路数。

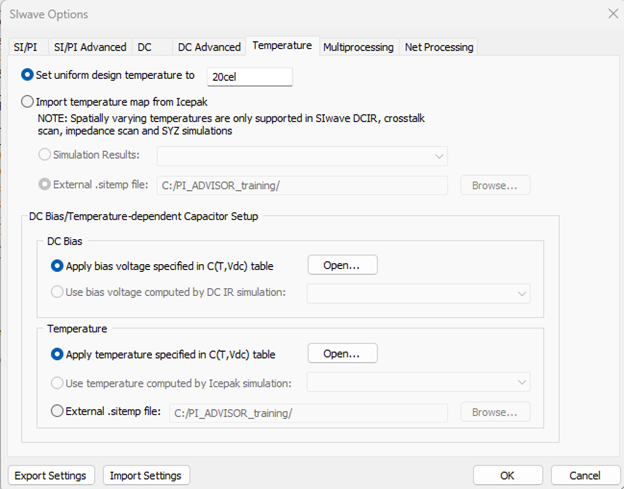

单击 temperature (温度) 选项卡,选择另一个将影响迹线电导率的温度。请注意,这里可以将温度分布从 Icepack 导入到模型中。只需指定 Icepack 文件名和该文件中的模拟名称即可。

图 12:高级选项 temperature 选项卡

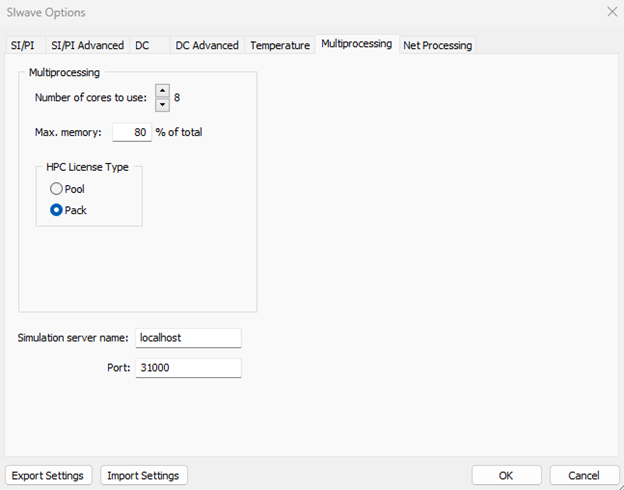

选择 Multiprocessing 以选择要使用的内核数和要使用的 RAM 百分比。

图 13:高级选项 Mutliprocessing 选项卡

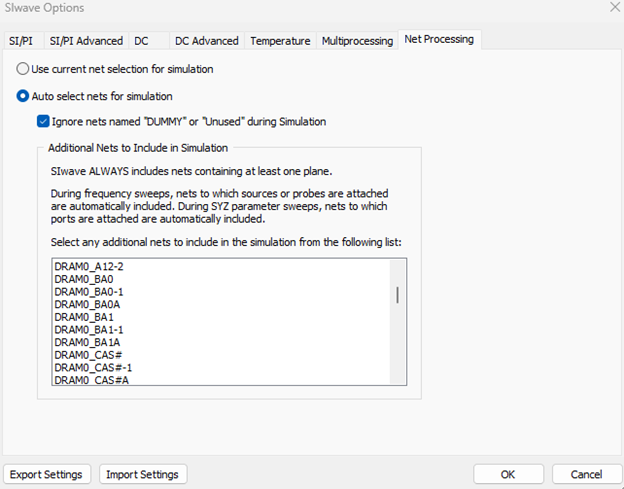

去网处理,更多选择。当然,如果用户想查看走线和电源层之间或电源层本身之间的串扰,用户可以在仿真中添加更多网络,例如接地和电源网络。

图 14:高级选项 “网络处理 ”选项卡

在启动求解器之前,请为解决方案命名,因为您需要执行许多解决方案。例如,在这里,将其命名为 FrequencyDomain_3GHz。

检查解决方案:

- 串扰分配

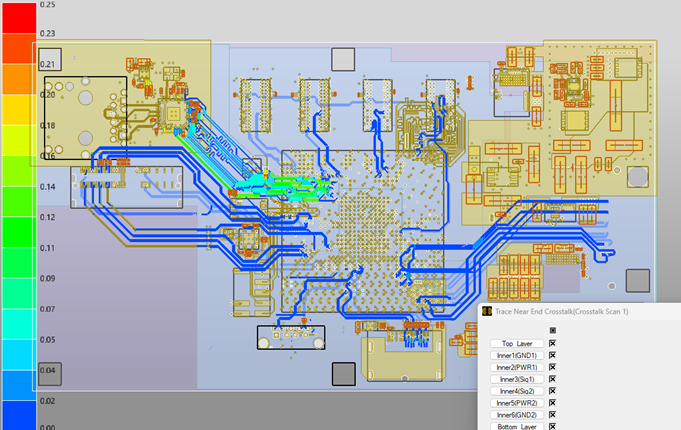

第一个结果是沿每条路径的串扰系数。侧面的刻度显示最差的串扰电平系数。显示所有迹线的近端或远端串扰。使用这些值的正确方法是首先确定哪条迹线的串扰不可接受,无论是近端还是远端,然后使用这些图来定位最薄弱的部分并尝试更好地隔离它们。

图 15:每条迹线的串扰电平 – NEXT 值

图 16:每条迹线的串扰电平 – FEXT 值

- 放大并将鼠标悬停在任何行上可查看任意点的值。请注意,它会告知这是 SE 还是差分跟踪。

- 更改比例,双击条形码,然后修改比例。如果存在显著变化,请选择对数刻度。

- 选择要显示的图层。

- 如果用户正在检查串扰并想知道这是哪条线路?在所有图层中激活追踪选项。现在,用户可以看到原始网络,放大并识别网络。

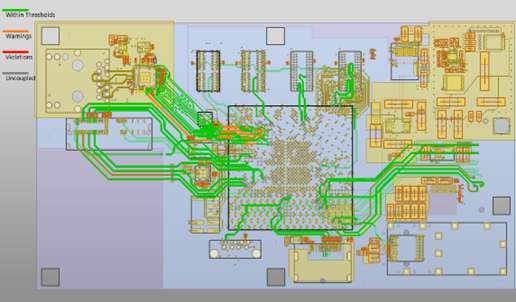

- 违规图

第二个结果甚至更好,因为求解器可以识别串扰与警告和违规级别交叉的位置。这样,设计人员可以更快地缩放不良区域。问题可能是接地不良、过孔不足、过渡不良、分离小和/或层厚大。

图 17:串扰违规

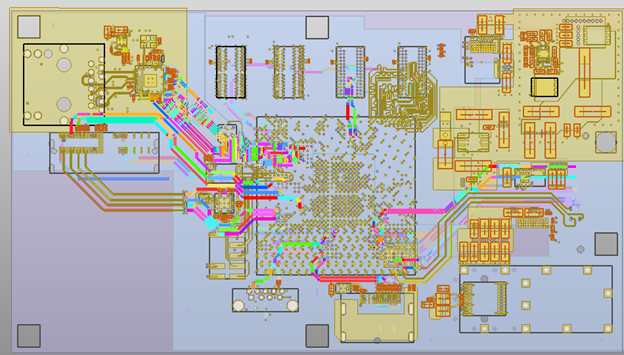

- 耦合结构

从串扰结果中,SIwave 检测走线的哪些部分不能被视为单个,而是与其他线路耦合。图中的颜色都是相对的。这些图是设置的函数。我们定义 setup 中的 crosstalk 和 coupled traces 的数量。

图 18:耦合条件

图 19:所有迹线每个部分的耦合度数

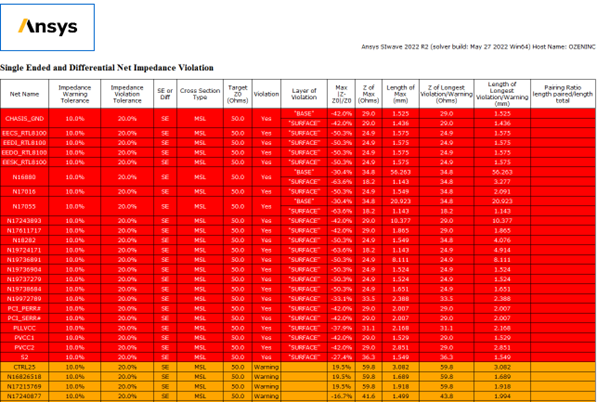

- 生成报告

SIwave 还可以将所有信息放在一个表格中。下表详细总结了所有调查结果。

图 20:串扰结果总结

- 修改跟踪。

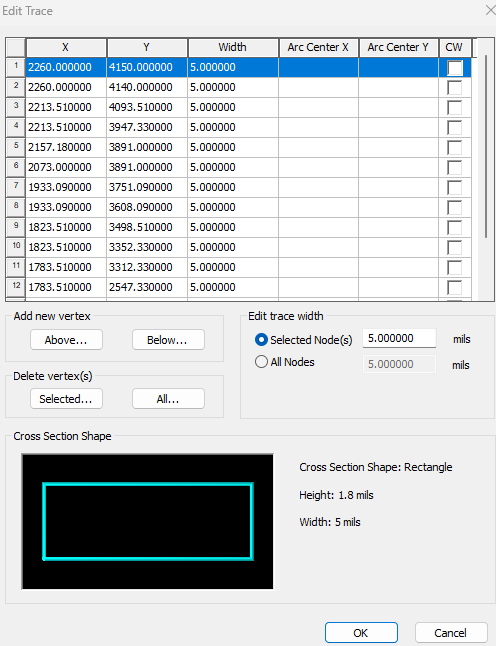

要修改任何轨迹,请单击它,选择 Centerline Edit,然后更改中心线的宽度和坐标。

图 21:如何修改跟踪

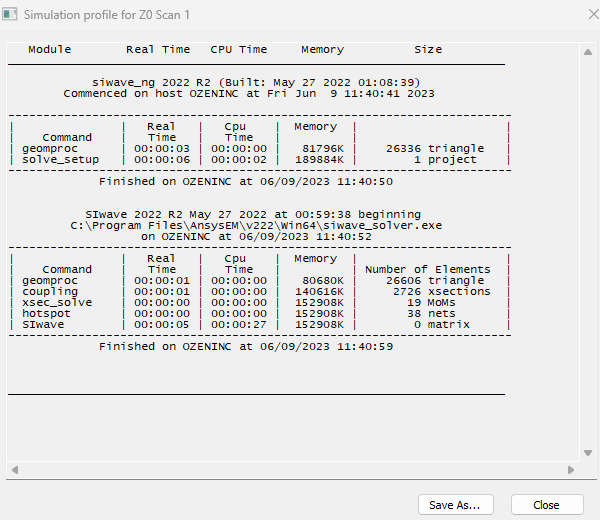

- 查看个人资料。

查看个人资料。

图 22:配置文件

- 串扰求解器 – 时域。

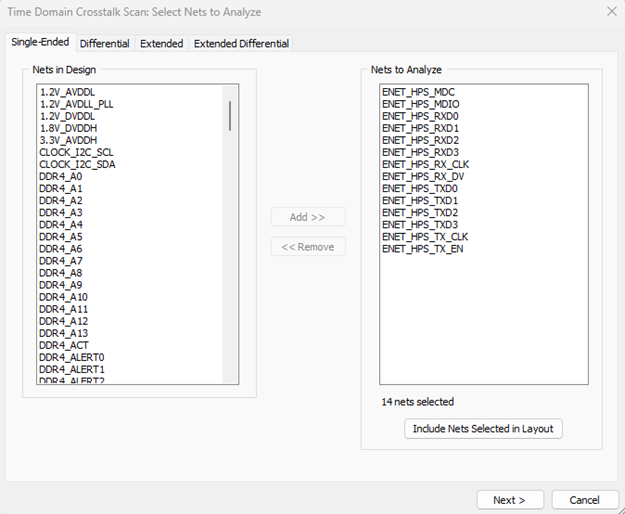

选择 Crosstalk Scan 求解器,然后选择时域选项。同样,另一个对话框。SIwave 使用所有跟踪填充左列。请注意 single 和 differential 的所有选项卡。选择要分析的行并将其移动到右列。按 Next(下一步)。

图 23:串扰 – 时域对话框

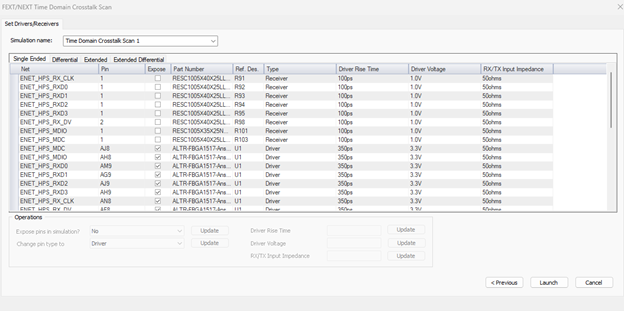

时域 1 类似于 TDR 分析。它从一侧发送信号,并读取其他端口上的信号。因此,需要指定每条迹线上使用的信号的上升时间和电压。上升时间定义了信号的带宽。填满表格后,我们启动求解器。

图 24:输入上升时间和电压电平

检查解决方案:

- Trace to Trace 串扰

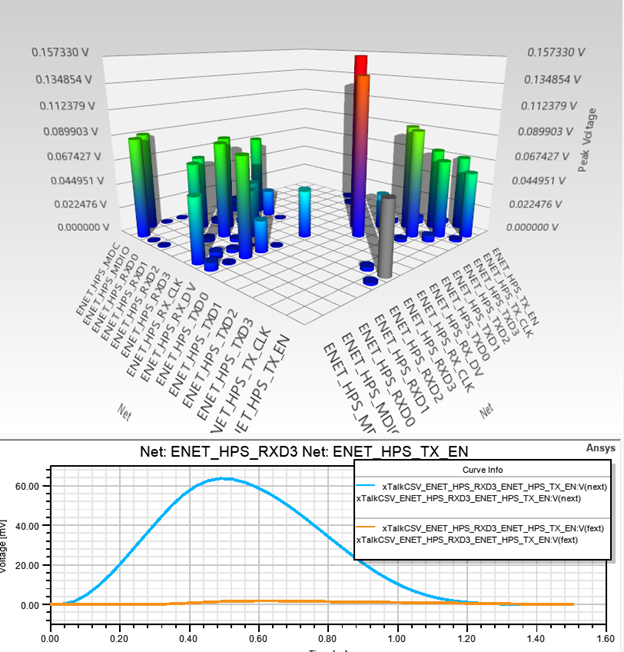

第一个结果是任意两条 traces 之间的串扰。如果点击任何条形,SIwave 将显示远端和近端串扰电压响应。在左侧条形图上,可以选择在条形图中显示远端或近端。条形图下的绘图始终包含两条曲线。

图 25:任意两条迹线(条形)和 TDR 之间的串扰沿一条迹线(曲线图)。

用户还可以在干扰线上添加输入和输出信号。您还可以为不同的 trace绘制许多 crosstalk 。用户这样做是为了进行比较。

图 26:任意两条迹线(条形)和 TDR 之间的串扰沿一条迹线(曲线图)。

因此,时域条显示最差的串扰电压。它还绘制了沿走线的串扰扩展。这就是绘制曲线与时间的原因。这里的时间相当于物理距离。时域结果使设计人员能够根据工作中使用的信号的上升时间了解预期的串扰。相比之下,此信息很难从 s 参数中实现。

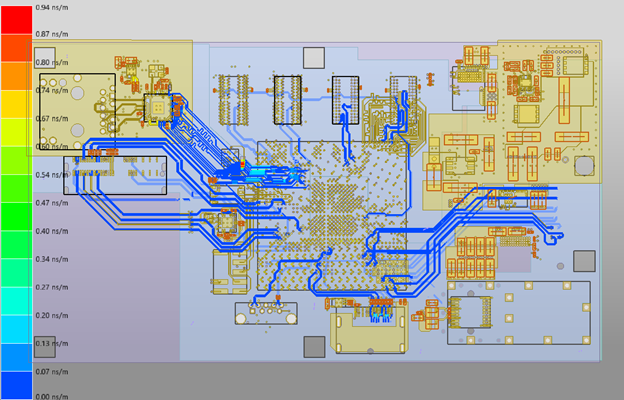

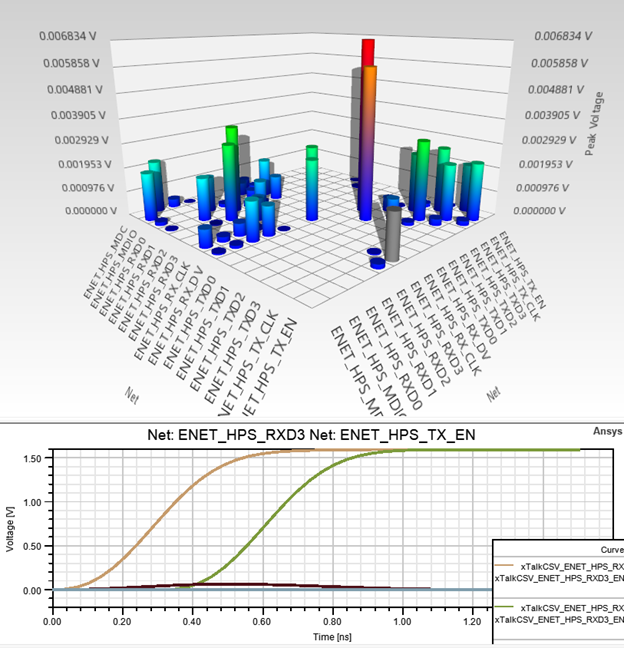

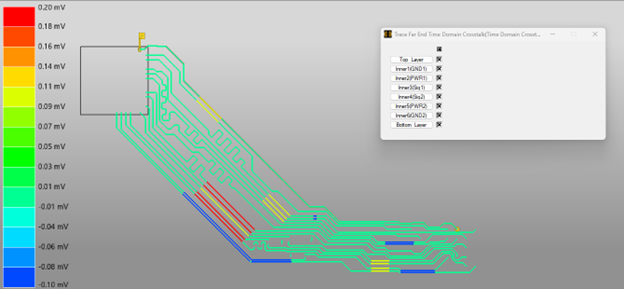

- 沿走线的串扰分布

与 Frequency domain 选项一样,时域可以预测沿任何走线的最差可能串扰的位置。但在时域中,SIwave 显示来自所有其他线路的所有电压的总和。此图突出显示了保护较弱的跟踪。也许大小并不能说明什么,但颜色可以帮助设计人员确定需要认真修改的区域。

图 27:每条迹线的串扰电平

- 耦合结构

根据串扰结果,SIwave 可以预测耦合截面。这意味着 SIwave 不能将跟踪视为红色部分中的单行。它们在 SIwave 中看起来就像是耦合的一样。

图 28:所有迹线每个部分的耦合度数

设计人员可以从 SYZ 求解器、频域和时域分析中学到很多关于 PCB 接地的知识。如果有任何问题,用户可以使用工具放大薄弱区域并修复它们。