为了解决这些问题,业界正积极寻求新的技术和标准,比如Compute Express Link (CXL),它旨在通过提供标准化的高速互连来提高内存带宽、降低延迟,并简化内存扩展的软件集成,从而有效地打破内存墙的限制。

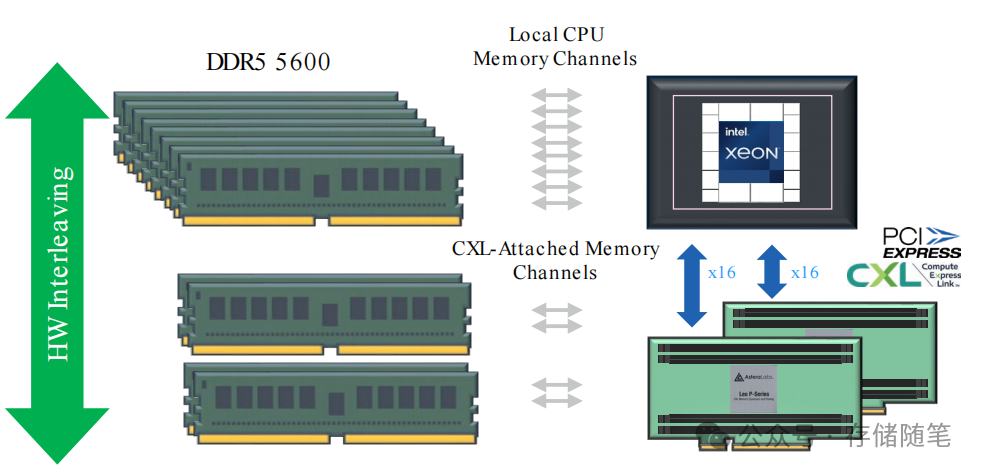

通过使用CXL(Compute Express Link)技术来突破内存墙,可以实现以下几项关键改进,比如一个CXL控制器厂商测试方案:

-

增加服务器内存带宽和容量50%:CXL通过提供一个高速、低延迟的互连标准,使得服务器能够外接更多的内存资源,而不局限于主板上的物理插槽。这样,服务器内存的带宽(数据传输速度)和容量得以显著提升,理论上可以达到现有配置的1.5倍,从而更好地满足高性能计算和大数据处理的需求。

-

降低延迟25%:CXL技术设计时考虑到了低延迟通信,使得处理器能够更快地访问外部扩展的内存资源,相较于传统外部存储或网络存储方案,访问时间减少约四分之一。这有助于减少数据等待时间,提升系统响应速度和整体计算效率。

-

使用标准DRAM以实现灵活的供应链和成本控制:CXL兼容标准DRAM技术,这意味着企业可以在全球供应链中选择更广泛的内存供应商,有利于成本控制和供应稳定。标准化还简化了内存的采购流程,减少了定制化硬件的成本,使内存升级和维护更加经济高效。

-

无缝扩展内存以支持现有和新应用:CXL使得内存资源可以根据实际应用需求动态扩展,无论是对于已有的传统应用还是新兴的内存密集型应用,如人工智能、大数据分析等,都能通过简单的硬件添加来提升内存支持,无需对软件架构做重大调整。这种扩展性保证了系统的未来适应性和灵活性,降低了技术更新换代的成本。

CXL技术为数据中心和高性能计算环境提供了一种有效的解决方案,它不仅提升了内存的性能和容量,而且通过标准化和低延迟特性,简化了系统集成和管理,最终帮助用户突破了内存墙的限制,实现了更高效的数据处理和应用性能。

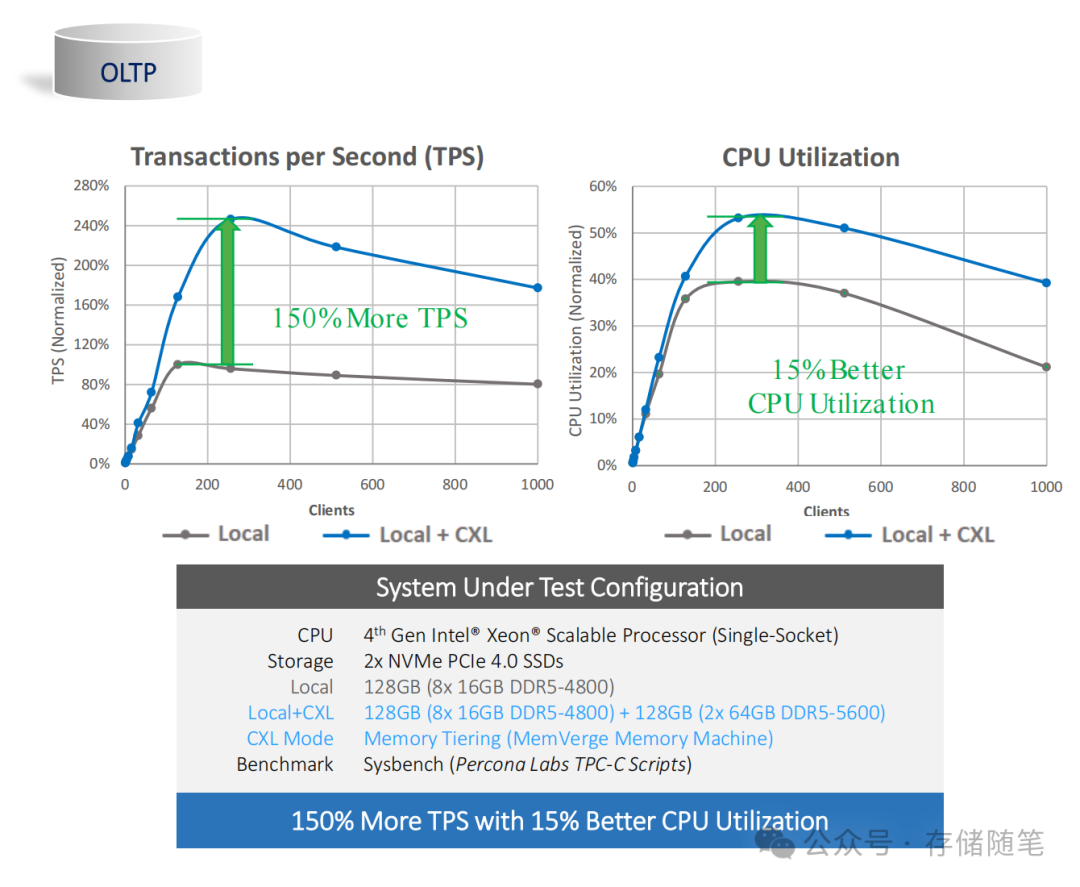

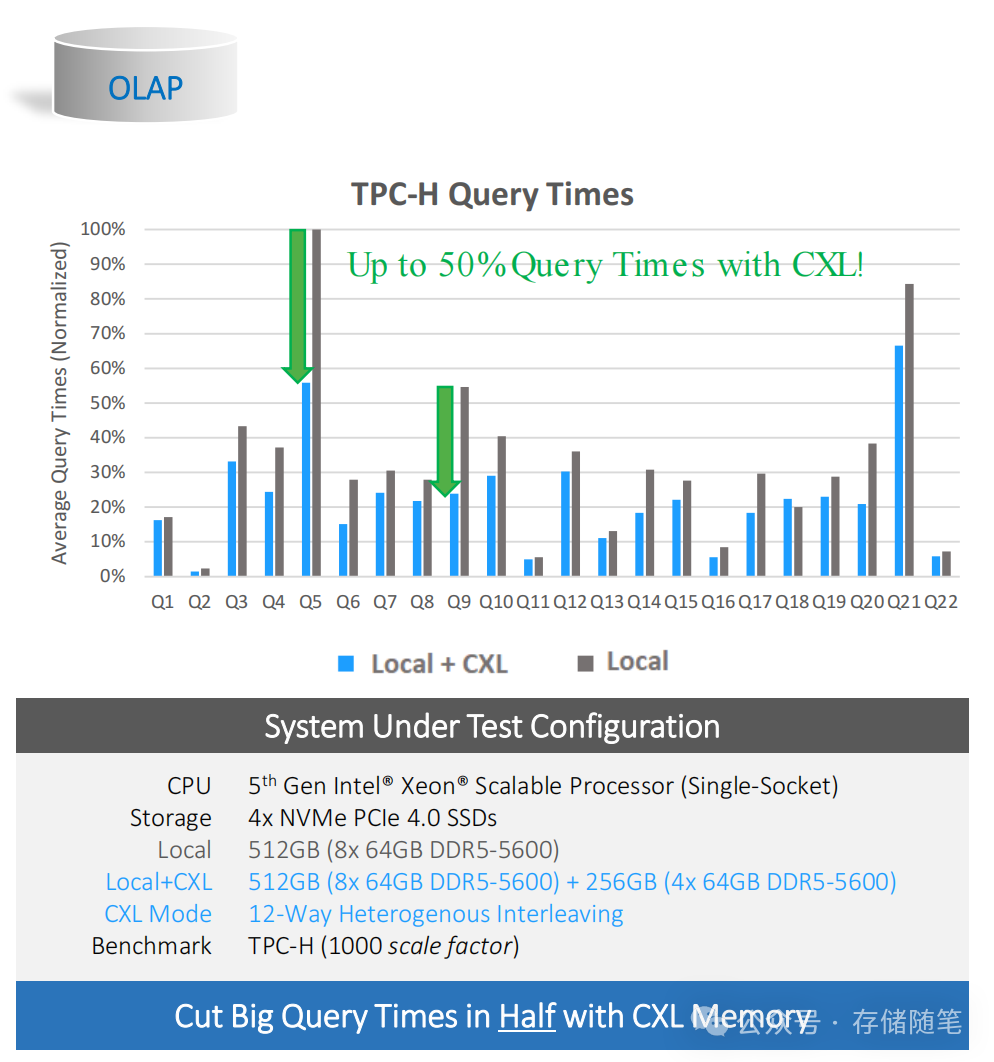

OLTP(Online Transaction Processing)与OLAP(Online Analytical Processing)是两种不同的数据库操作类型,它们在处理数据和目标上有所区别,而CXL(Compute Express Link)技术在这两种场景下的应用结果展示出了显著的性能提升。

OLTP通常涉及大量并发的小型事务,如银行交易、电子商务订单等,侧重于数据的插入、更新和删除操作,要求极高的事务处理速度和数据一致性。使用CXL内存的测试结果显示,与仅使用本地DDR5-5600内存的系统相比,使用CXL内存和MemVerge Memory Machine进行内存分层后,事务处理能力(TPS)提高了150%,同时CPU利用率提高了15%。

OLAP则是面向数据分析,主要用于复杂的查询和报告,侧重于从大量历史数据中提取信息,进行汇总、分析和预测,如商业智能报表。在OLAP测试中,与仅使用本地DDR5-5600内存的系统相比,结合CXL内存的系统在处理TPC-H(采用1000规模因子)时,能够显著降低大查询时间,几乎减半。

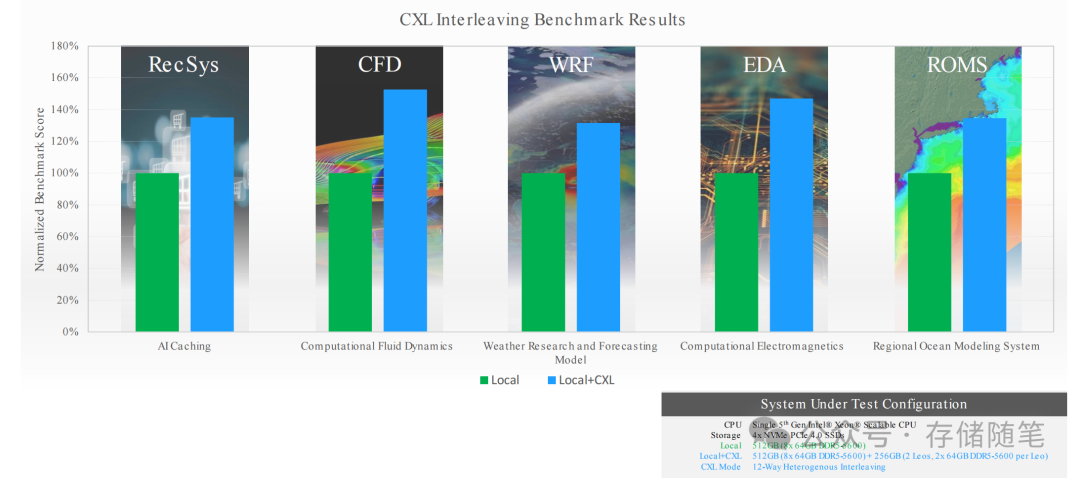

CXL在多个应用领域都有很好的应用前景,比如计算流体动力学(Computational Fluid Dynamics, CFD)、天气研究与预报(Weather Research and Forecasting, WRF)、计算电磁学(Computational Electromagnetics)、区域海洋建模系统(Regional Ocean Modeling System, ROMS)等应用,这些应用往往需要处理大量数据并行计算。

CXL通过内存扩展,使得每个插槽的内存容量可以增加至2.33倍,同时内存带宽提升1.66倍,这对于内存密集型应用来说,意味着可以处理更大数据集而不会受到传统内存限制。

CXL作为一种内存互连技术,对于应对现代数据密集型应用的挑战,尤其是内存墙问题,提供了有效的解决方案。

-

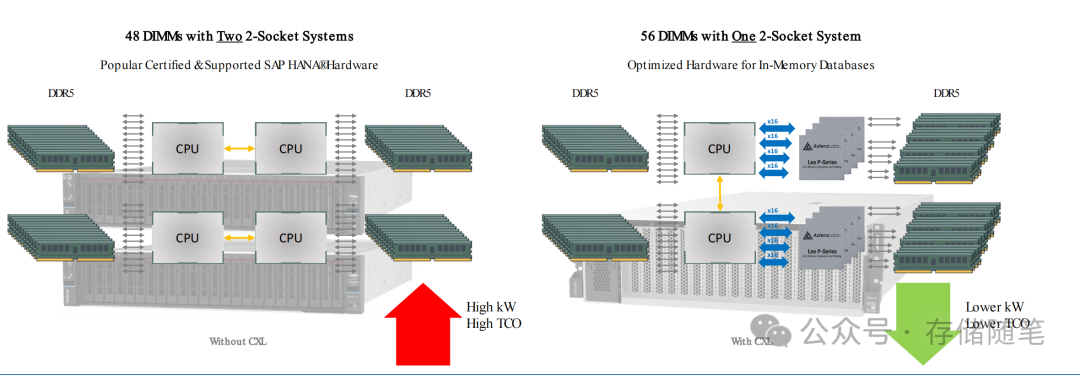

这对于如SAP HANA这样的内存数据库系统尤为重要,它原本可能受限于服务器DIMM插槽数量,但通过CXL,可以用更少的双路系统达到更高的内存配置,降低了总体拥有成本(TCO)并减少了能耗。

-

在AI推理和复杂的推荐引擎中,CXL内存扩展提供了足够的内存带宽和低延迟,以支持快速的数据处理和模型查询,提升用户体验。

参考文献:

1.https://computeexpresslink.org/wp-content/uploads/2023/12/CXL_3.1-White-Paper_FINAL.pdf

2.https://www.rambus.com/blogs/compute-express-link/

3.CXL Smart Memory Controllers:《Breaking Through the Memory Wall with CXL》

如果您看完有所受益,欢迎点击文章底部左下角“关注”并点击“分享”、“在看”,非常感谢!

精彩推荐:

-

磁带存储:“不老的传说”依然在继续

-

浅析3D NAND多层架构的可靠性问题

-

SSD模拟器MQSim简介与资料分享

-

孙凝晖院士万字长文|人工智能与智能计算的发展

-

探究NVMe SSD HMB应用场景与影响

-

深度剖析:大容量QLC SSD为何遭疯抢?

-

SSD突然掉电,是谁保护了用户数据?

-

漫谈HAMR硬盘的可靠性

-

万物皆可计算|下一个风口:近内存计算

-

SSD数据错误如何修复?

-

CXL与PCIe世界的尽头|你相信光吗?

-

全景剖析SSD SLC Cache缓存设计原理

-

存储革新:下一代低功耗PCM相变存储器

-

3D DRAM虽困难重重,最快明年到来

-

字节跳动入局存储内存SCM

-

PCIe 7.0|不要太卷,劝你先躺平

-

SSD LDPC软错误探测方案解读

-

关于SSD LDPC纠错能力的基础探究

-

存储系统如何规避数据静默错误?

-

PCIe P2P DMA全景解读

-

深度解读NVMe计算存储协议

-

对于超低延迟SSD,IO调度器已经过时了吗?

-

浅析CXL P2P DMA加速数据传输的原理

-

HDD回暖于2024,与SSD决战于2028

-

FIO测试参数与linux内核IO栈的关联分析

-

NVMe over CXL技术如何加速Host与SSD数据传输?

-

浅析LDPC软解码对SSD延迟的影响

-

为什么QLC NAND才是ZNS SSD最大的赢家?

-

SSD在AI发展中的关键作用:从高速缓存到数据湖

-

浅析不同NAND架构的差异与影响

-

SSD基础架构与NAND IO并发问题探讨

-

字节跳动ZNS SSD应用案例解析

-

CXL崛起:2024启航,2025年开启新时代

-

NVMe SSD:ZNS与FDP对决,你选谁?

-

浅析PCI配置空间

-

浅析PCIe系统性能

-

存储随笔《NVMe专题》大合集及PDF版正式发布!

如果您也想针对存储行业分享自己的想法和经验,诚挚欢迎您的大作。

投稿邮箱:Memory_logger@163.com (投稿就有惊喜哦~)

《存储随笔》自媒体矩阵

更多存储随笔科普视频讲解,请移步B站账号:

如您有任何的建议与指正,敬请在文章底部留言,感谢您不吝指教!如有相关合作意向,请后台私信,小编会尽快给您取得联系,谢谢!