第六章处理器架构2的内容如下:

1.异或

实现异或,等价于与非&或:

# 异或等价于与非&或

MOV|in|1

MOV|in|2

NAND

MOV|3*8|4

OR

MOV|3*8|5

MOV|4*8|1

MOV|5*8|2

AND

MOV|3*8|out2.8位异或

对两个单字节输入执行按位异或(XOR):

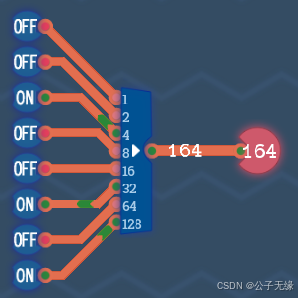

3.8位常数

高低电平搭配使得始终输出164:

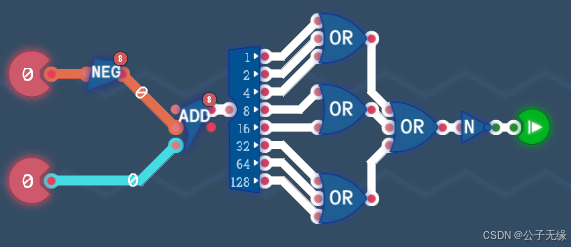

4.相等

判断两个数相等,可以将一个数取反,与另一个数相加,结果为0则相等:

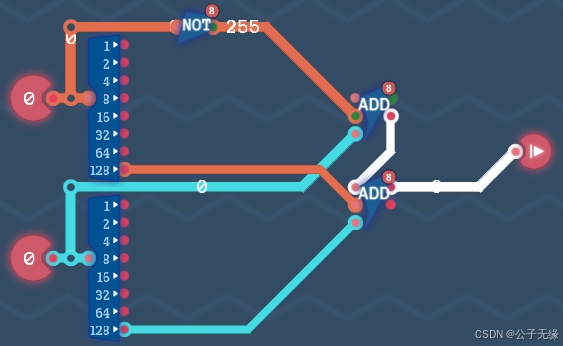

5.无符号小于

无符号判断的思路跟上面判断相等类似:

6.有符号小于

有符号小于需要额外加入最高位补码(负号)的判断

7.宽指令

偶数时刻存储,奇数时刻一次输出两个值:

8.一把线,像挂面

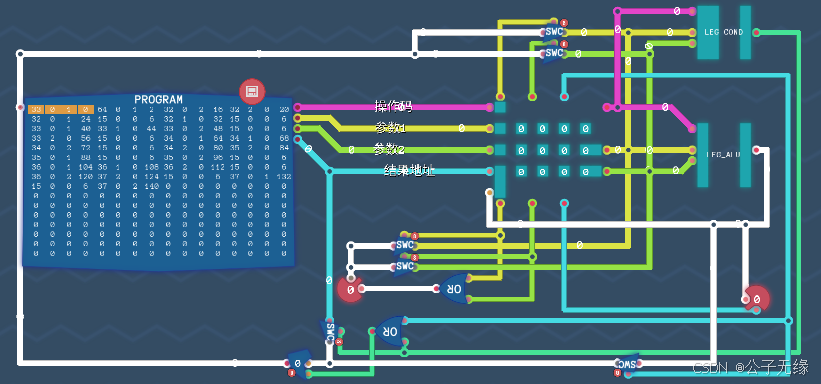

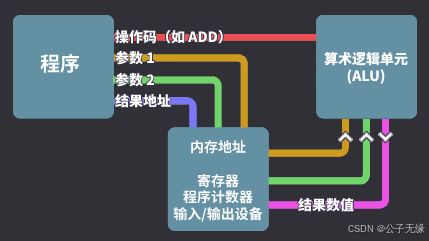

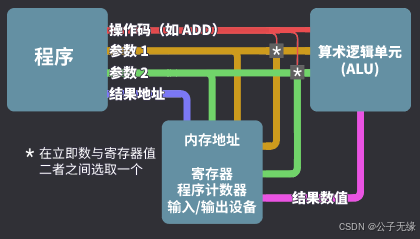

前面都是小打小闹,这一关真正是走上了LEG架构之路。LEG架构如下图所示:

注意,这一关里操作码(OPCODE)始终是0,这意味着我们将对参数1和参数2做加法(ADD),并将结果发送到目标地址上。命令的输入参数和输出参数都是地址值。地址值与元件的对应关系如下所示:

| 地址值 | 元件 |

| 0 | 0号寄存器 |

| 1 | 1号寄存器 |

| 2 | 2号寄存器 |

| 3 | 3号寄存器 |

| 4 | 4号寄存器 |

| 5 | 5号寄存器 |

| 6 | 计数器 |

下面来实现这一关的功能:

(1)首先准备构建上面的内存地址模块 RegisterGroup,里面包含了寄存器、程序计数器与输入/输出设备:

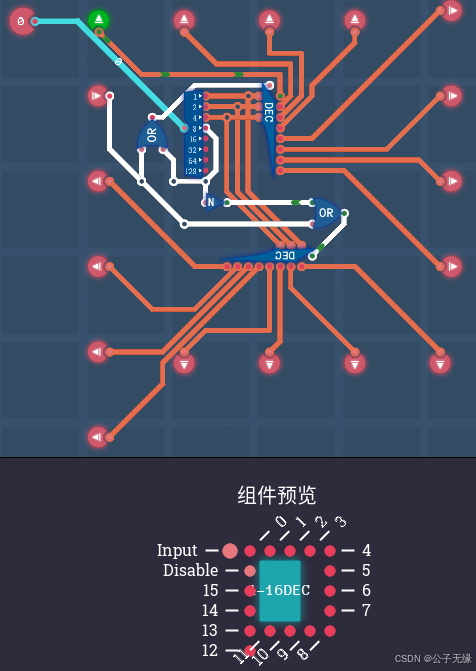

先封装一个4-16的译码器 4-16DEC 元件,取8位输入低四位,译码为0-15的十进制数输出:

再封装一个寄存器两路控制输出 Register2Out 元件,使能加载1则输出1,使能加载2则输出2:

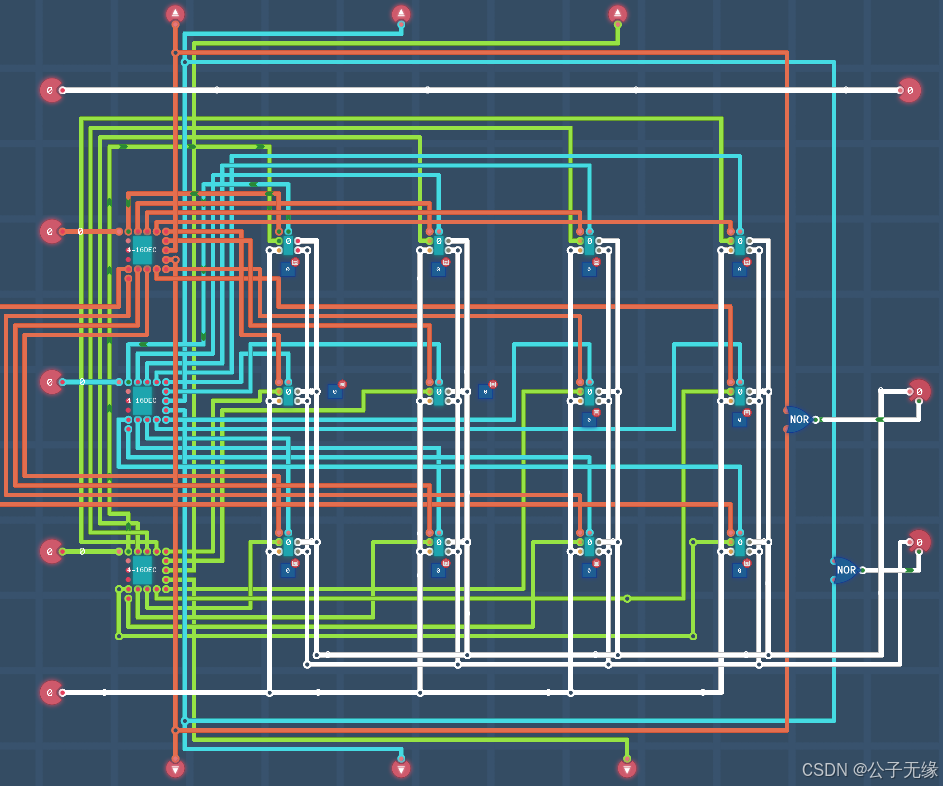

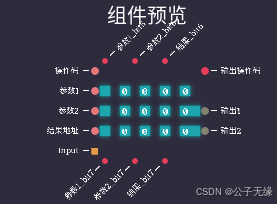

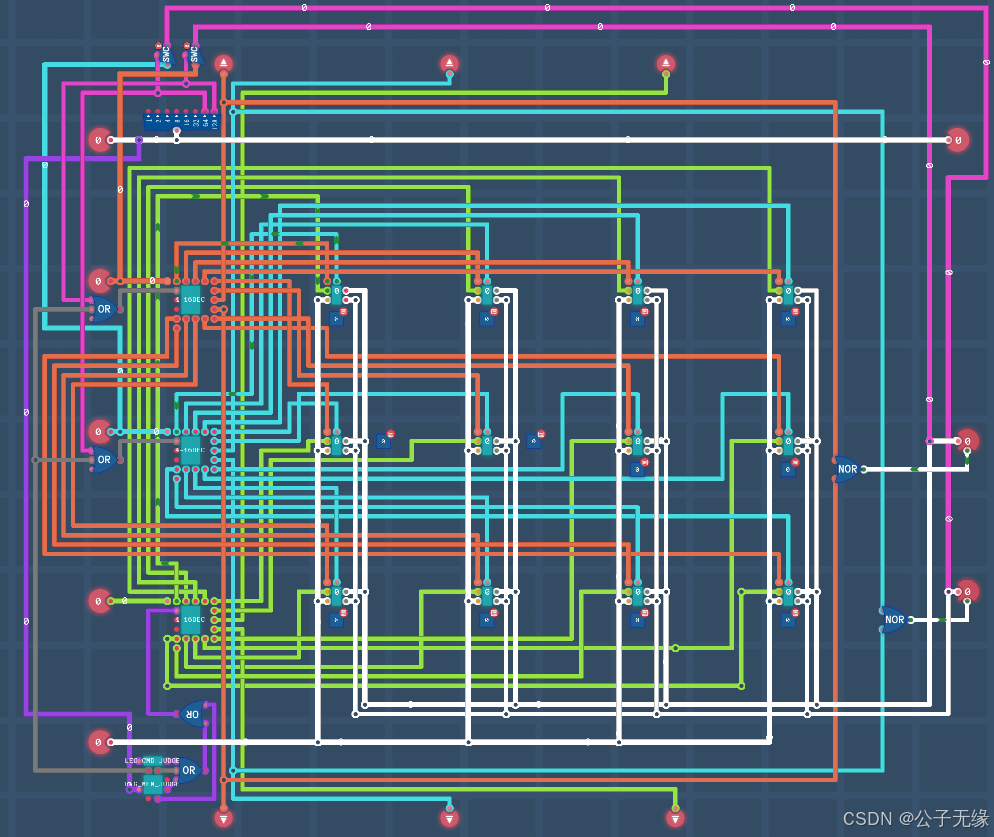

构建内存地址模块 RegisterGroup ,其中,左边一列作为输入,从上到下分别为操作码、参数1、参数2、结果地址、输入使能;右边一列作为输出,从上到下分别为输出操作码、输出1、输出2;上面一行为参数1_bit6、参数2_bit6、结果_bit6;下面一行为参数1_bit7、参数2_bit7、结果_bit7。主要实现将参数1(橙色线路)、参数2(蓝色线路)、地址(绿色线路)通过4-16DEC元件解码之后,控制12个Register2Out元件

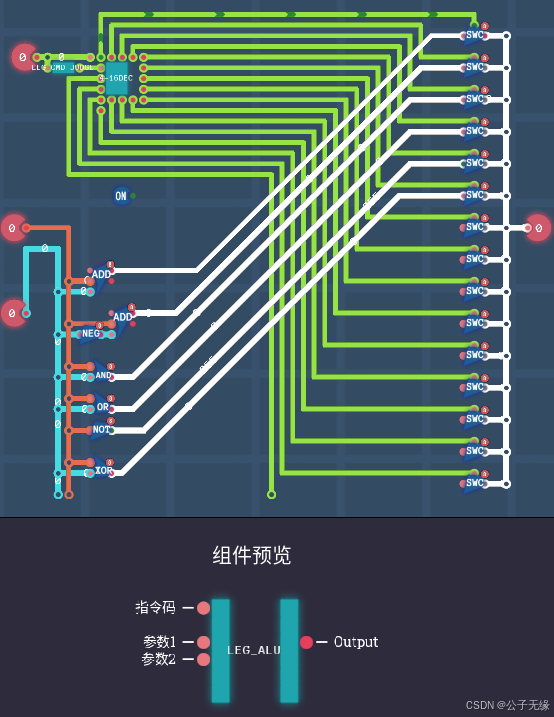

(2)实现LEG架构的算术逻辑单元LEG_ALU。

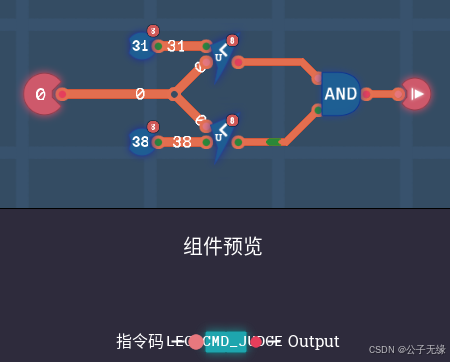

先封装一个 LEG_CMD_JUDGE 元件,用来根据指令码判断执行算术逻辑单元ALU还是条件跳转单元COND:

再通过4-16DEC元件解析收到的指令码,并执行相关计算:

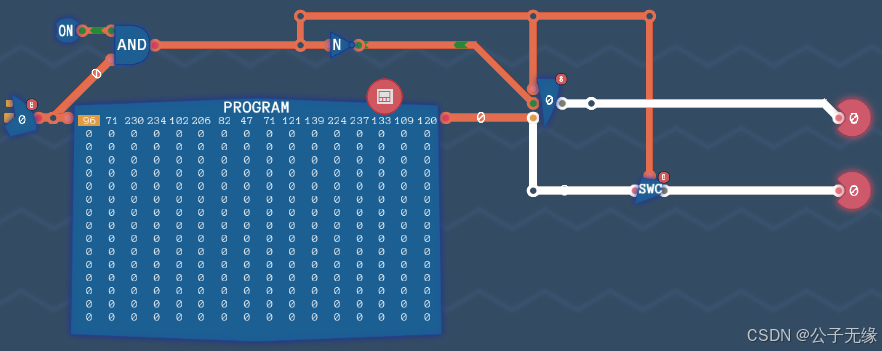

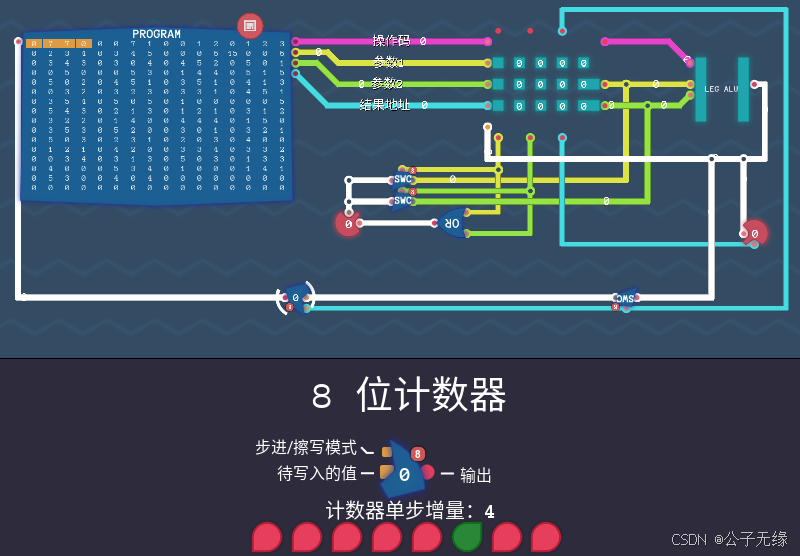

(3)组装程序体PROGRAM 、内存地址模块RegisterGroup、算术逻辑单元LEG_ALU,实现一个LEG的基础架构,通过计数器设定运算步长4:

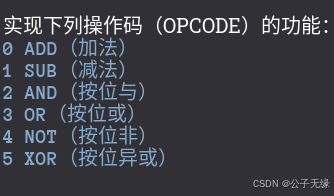

9.操作码

上面的LEG_ALU已经实现了这一关下面几种操作码的功能,不再重复。

10.立即数

新增立即数功能,即当操作码的第8位为1时,将参数1作为立即数(而非地址值);当操作码的第7位为1时,将参数2作为立即数(而非地址值):

首先需要调整一下之前的寄存器组处理模块RegisterGroup,使其加上立即数功能,即上图中标*的两根线,重新命名为RegisterGroup_IMM,在之前的模块中新增右上角紫色部分(指令码进来之后取第7、第8位作为开关,使能参数2、参数1直接用作模块输出,输入输出端口封装不变)。

注意其中左下角的两个小模块包括其周边电路暂时都不需要,是后面关卡的内容,可以按需删除或者参考我后面的文章提前完成:

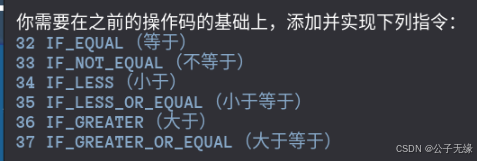

11.条件判断Ⅱ

新增条件判断模块。在之前的指令中,4个字节分别代表操作码、参数1、参数2、结果地址。而对于条件判断模块,4个字节分别代表操作码、参数1、参数2、跳转地址。其中操作码分为以下几种:

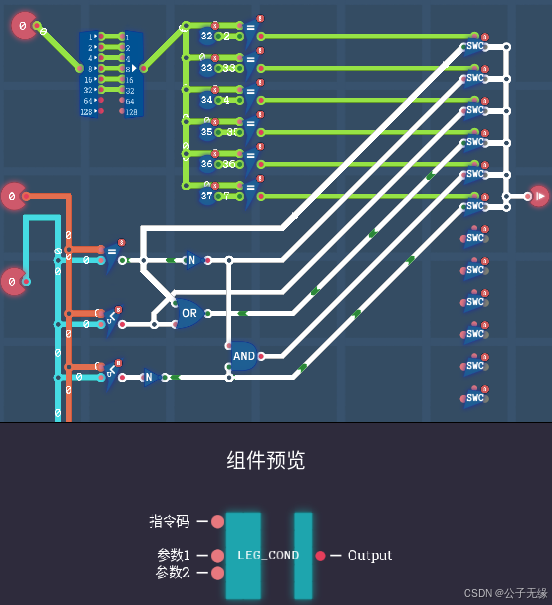

那么需要增加基于LEG架构的条件判断单元 LEG_COND,封装如下:

将条件判断模块LEG_COND与之前的算术计算模块LEG_ALU并联到系统中,加入开关筛选数据输出: