文章目录

- 1.R52+

- 2.ARM基本概念

- 2.1.指令集

- 2.2.执行状态(Execution State)

- 2.2.1AArch64

- 2.2.2AArch32

- 2.3. 指令集

- 2.4.寄存器

- 2.4.1系统寄存器

- 2.4.2特殊寄存器

- 2.5.异常等级(Exception Levels)

- 3.ARM汇编语言模块示例

- 4. ARM汇编指令集

记录ARM V8相关的学习笔记。

1.R52+

第一个Cortex-R处理器,如Cortex-R5,是建立在Armv7-R架构上的。R52和R52+是Armv8-R架构。

2.ARM基本概念

ARM公司发布的第一代支持64位处理器的指令集和体系结构,对ARMv7的具有兼容性。

2.1.指令集

使用RISC(精简指令集),具有以下RISC特点:

- 一组统一的寄存器;

- 一种加载/存储体系结构,其中数据处理操作只对寄存器内容进行操作,而不是直接对内存内容进行操作;

- 采用简单的地址模式(内容映射等),仅从寄存器内容和指令字段确定所有加载/存储地址。

2.2.执行状态(Execution State)

可以理解为两个执行容器,根据实际情况可以完成切换。

具体可参考DDI0487D_Architecture Reference Manual ARMv8-A architecture. pdf文档的“A1.3.1 Execution state”。

2.2.1AArch64

- 提供31个64位的通用寄存器。

- 提供64位的程序计数寄存器PC、栈指针寄存器SP以及异常链接寄存器ELR。

- 提供A64指令集。

- 定义ARMv8异常模型,支持4个异常等级,ELO~EL3

- 提供64位的内存模型。

- 定义一组处理器状态(PSTATE)用来保存PE的状态。

2.2.2AArch32

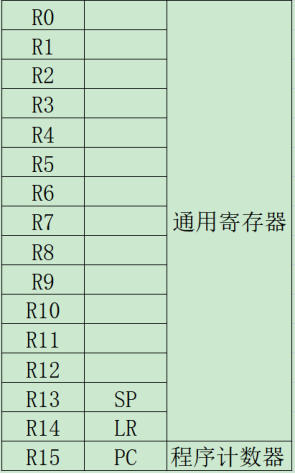

- 提供13个32位的通用寄存器,在加上程序计数器PC、栈指针寄存器SP、链接寄存器LR

- 支持两套指令集,分别是A32\T32(Thumb)指令集

- 支持ARMV7 - A模型,基于PE模式并映射到ARMv8的异常模型中

- 提供32位的模拟内存访问机制

- 定义一组处理器状态(PSTATE)用来保存PE的状态。

2.3. 指令集

ARMv8架构根据不同的执行状态提供不同指令集的支持。

- A64指令集:运行在AArch64状态,提供64位指令集支持。

- A32指令集:运行在AArch32状态,提供32位指令集支持。

- T32指令集:运行在AArch32状态,提供16和32位指令集支持。

2.4.寄存器

2.4.1系统寄存器

AArch64运行状态支持31个64位的通用寄存器,分别是x0~x30寄存器。

X0~X30:通用寄存器

SP:栈指针寄存器

PC:程序计数寄存器

而AArch32运行状态支持16个32位的通用寄存器。

15个通用寄存器R0~R14,一个程序指针PC寄存器

处理器状态(Processor State)

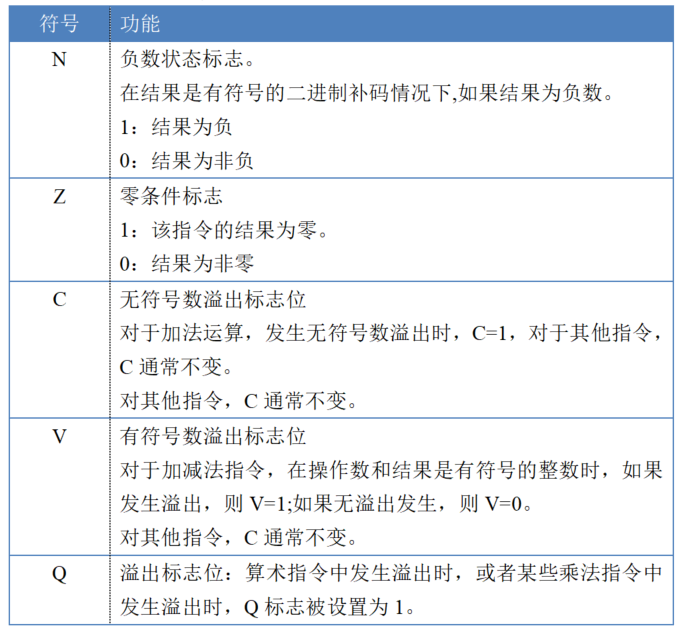

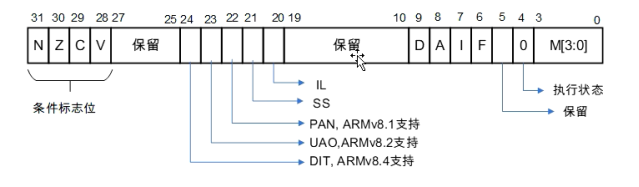

在ARMv7架构中使用CPSR寄存器来表示当前处理器的状态,而在AArch64里使用处理器状态寄存器来表示,简称PSTATE条件标志位(The Condition flags)

参考:“B1.2.2 Process state, PSTATE”,部分条件标志位如下:

具体系统寄存器可参考DDI0487D_Architecture Reference Manual ARMv8-A architecture. pdf文档的“D12 AArch64 System Register Descriptions”。

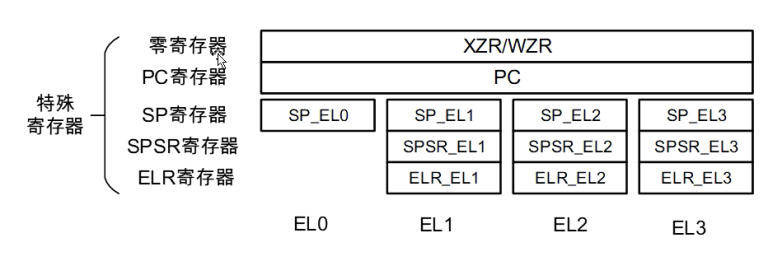

2.4.2特殊寄存器

零寄存器:寄存器值全为0,其中XZR是64bit,WZE是32bit

SP寄存器:栈指针,SP_EL0SP_EL3分别是EL0EL3下的栈指针寄存器

SPSR寄存器:保存处理状态寄存器(Saved Process Status Register),类似ARMv7的CPSR寄存器。

2.5.异常等级(Exception Levels)

异常等级确定了处理器当前运行的特权级别,类似ARMv7架构中特权等级。

- EL0:用户特权,用于运行普通用户程序(用户态)。

- EL1:系统特权,通常用于运行操作系统(内核态)。

- EL2:运行虚拟化扩展的虚拟监控程序(Hypervisor)。

- EL3:运行安全世界中的安全监控器(Secure Monitor) 。

参考“D1.1.1 Typical Exception level usage model”

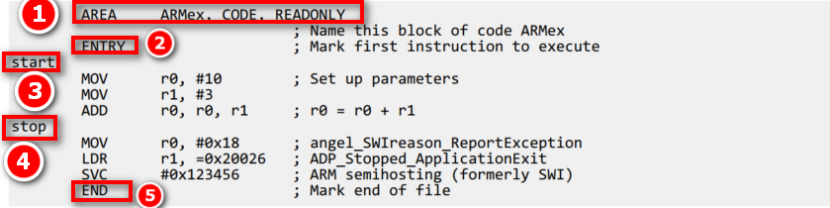

3.ARM汇编语言模块示例

ARM汇编语言模块由以下几个部分组成:

①ELF sections (defined by the AREA directive).

②Application entry (defined by the ENTRY directive).

③Application execution.

④Application termination.

⑤Program end (defined by the END directive)

4. ARM汇编指令集

ARM V8 A32常用指令集