软件安装:QuartusLite安装说明及驱动更新

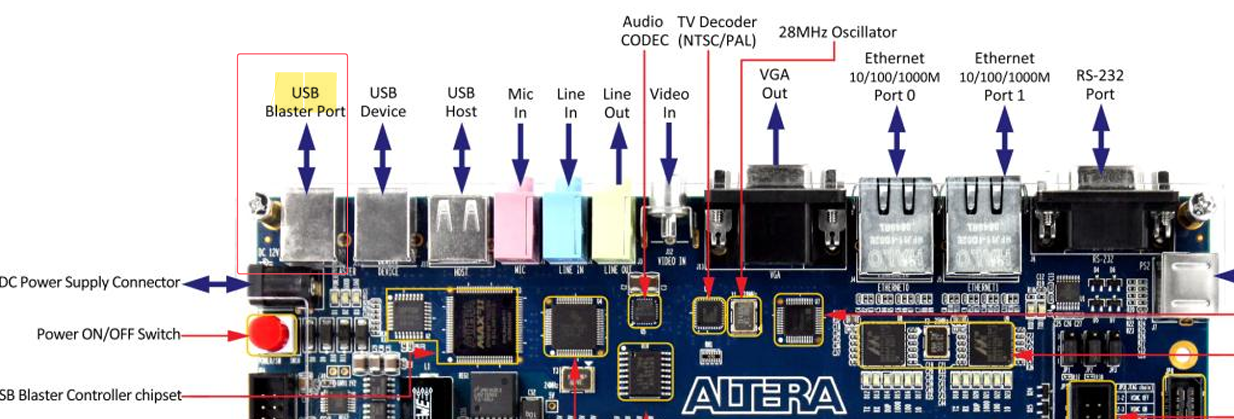

DE2-115上电及程序烧录

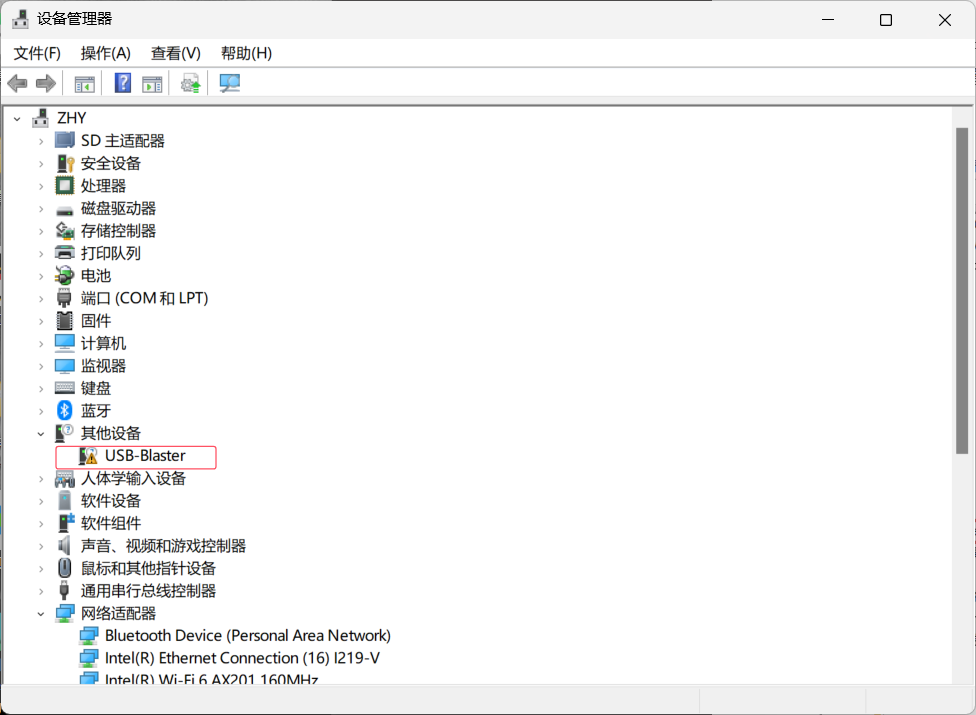

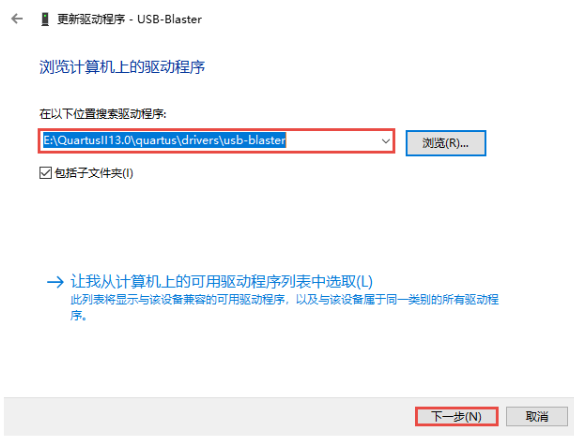

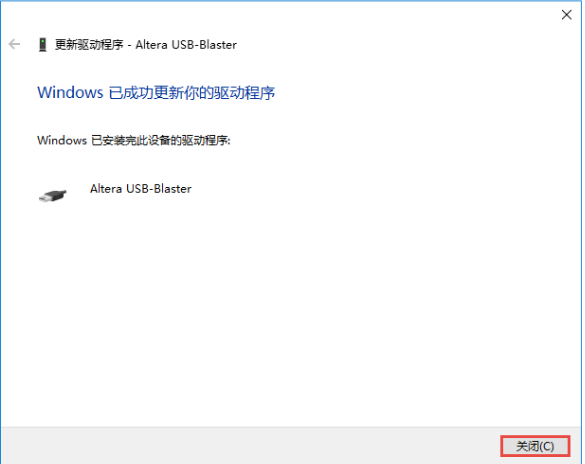

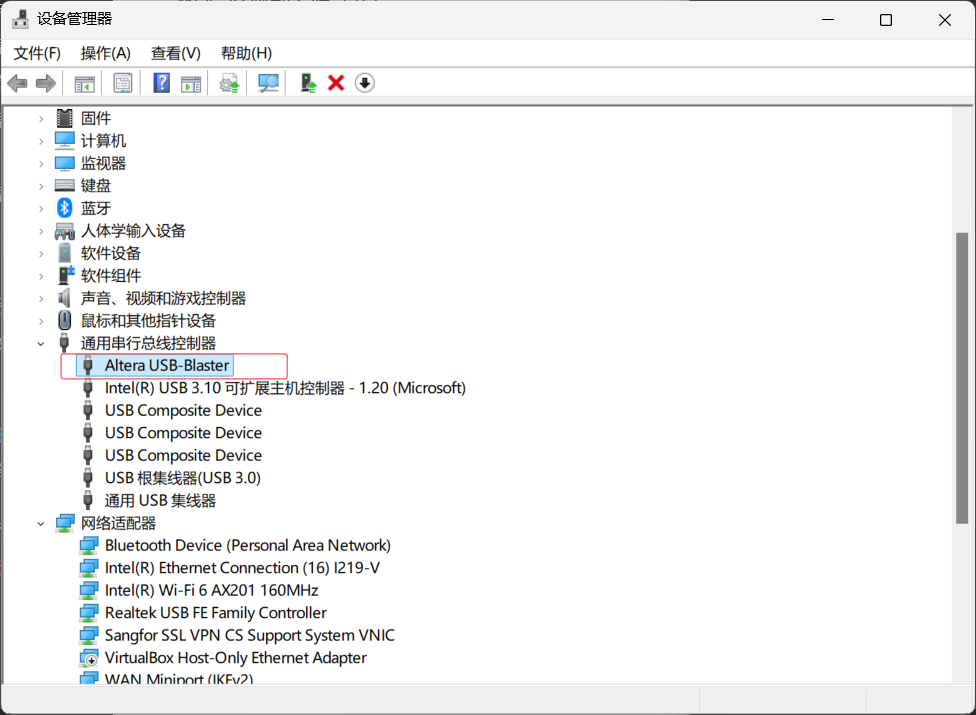

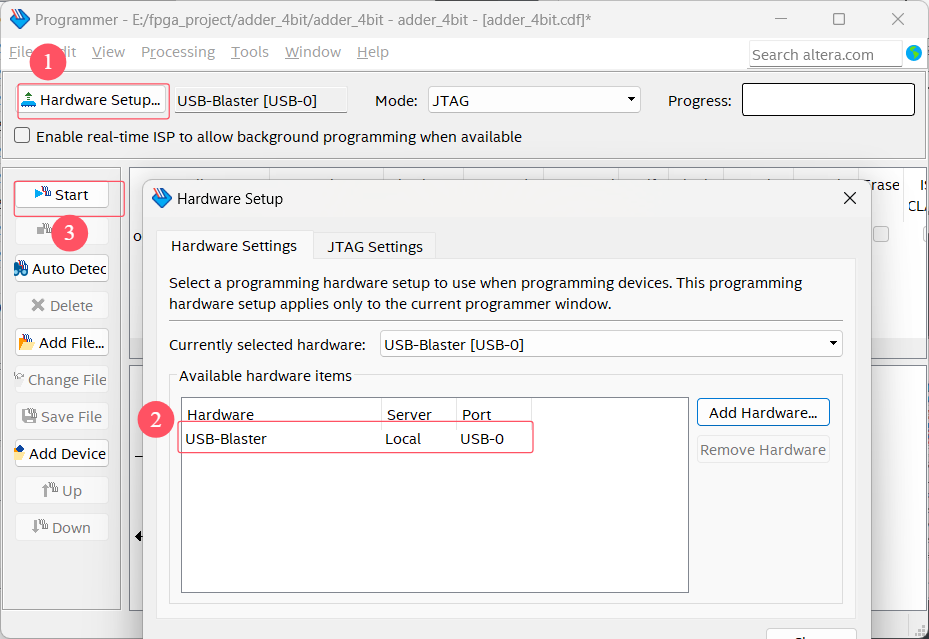

1.用包装盒里的USB 电缆将PC的USB端口和DE2-115开发板的USB Blaster连接器连接 起来,为了实现主机和开发板之间的通讯,必须安装USB Blaster 驱动软件

鼠标右击“USB-Blaster”选择“更新驱动程序(P)”

2.在将12V的适配器连接到DE2-115主板前,按下红色的ON/OFF开关确保电源断开。

3.按下DE2-115主板上红色的电源开关OFF /ON重新上电,将DE2-115开发板的拨码开关SW19由PROG拨到RUN,就可以烧写程序了

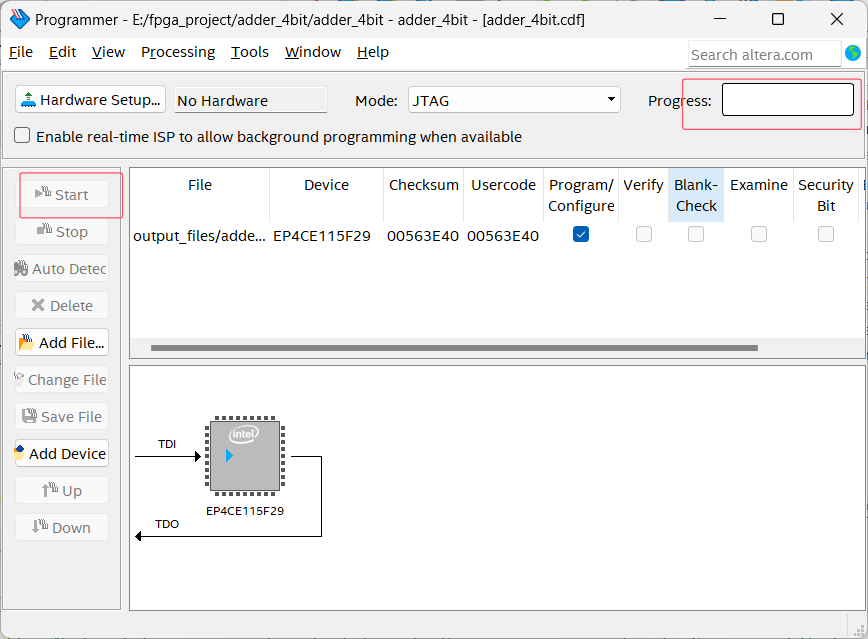

在烧录的时候我们直接点击 start,当右面的进程到达 100% 就说明已经烧录成功了:

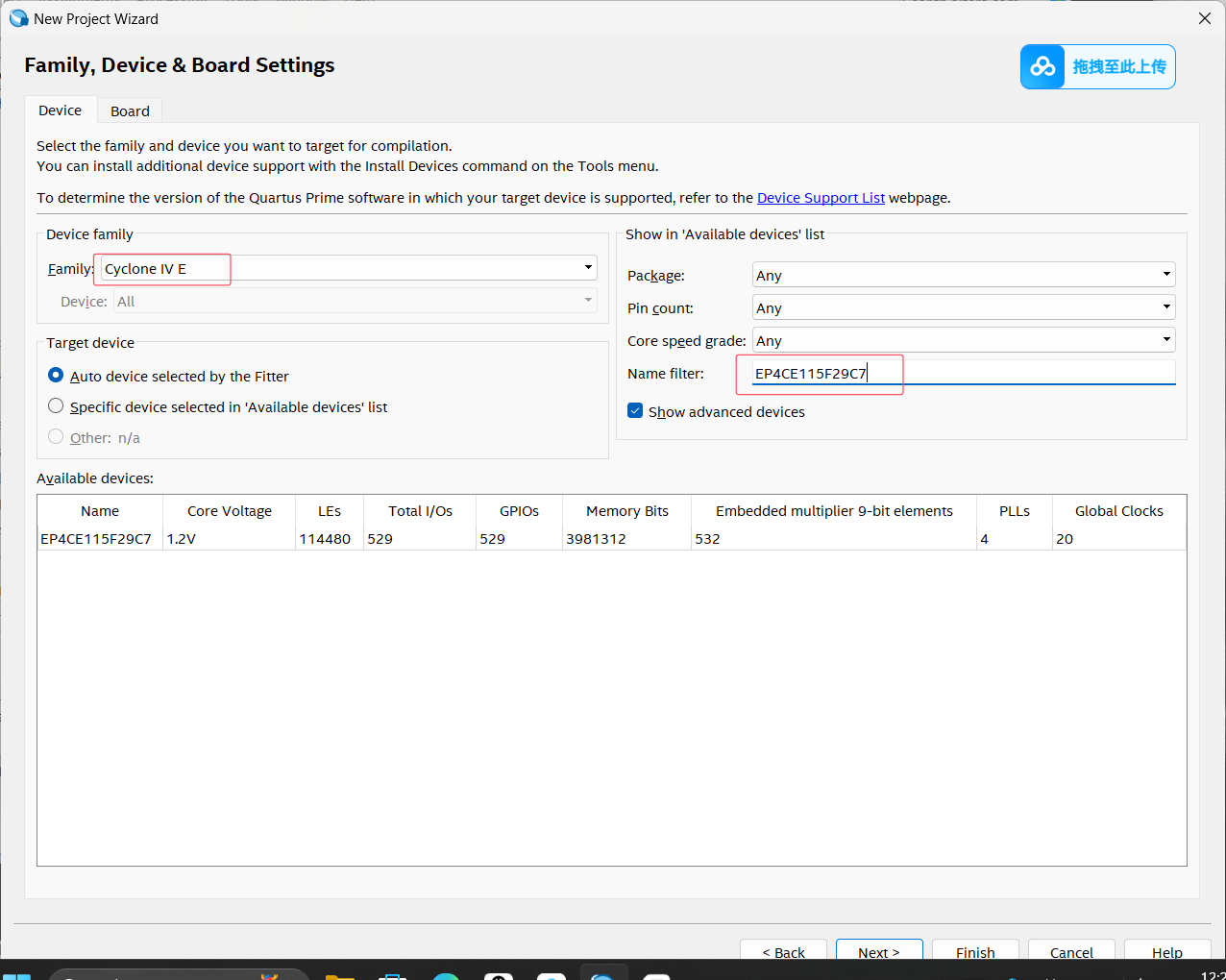

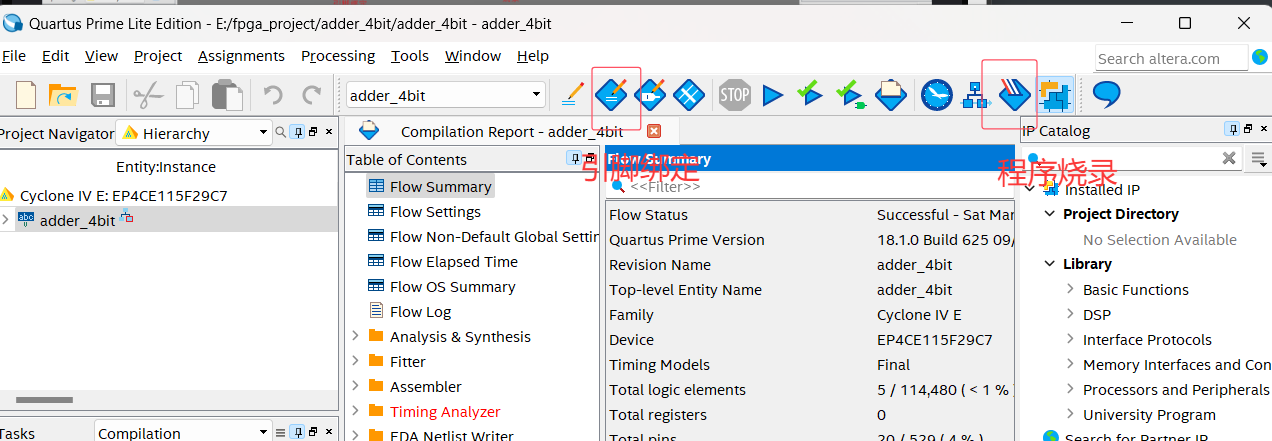

这里选择 Cyclone IV E 的 EP4CE115F29C7 芯片

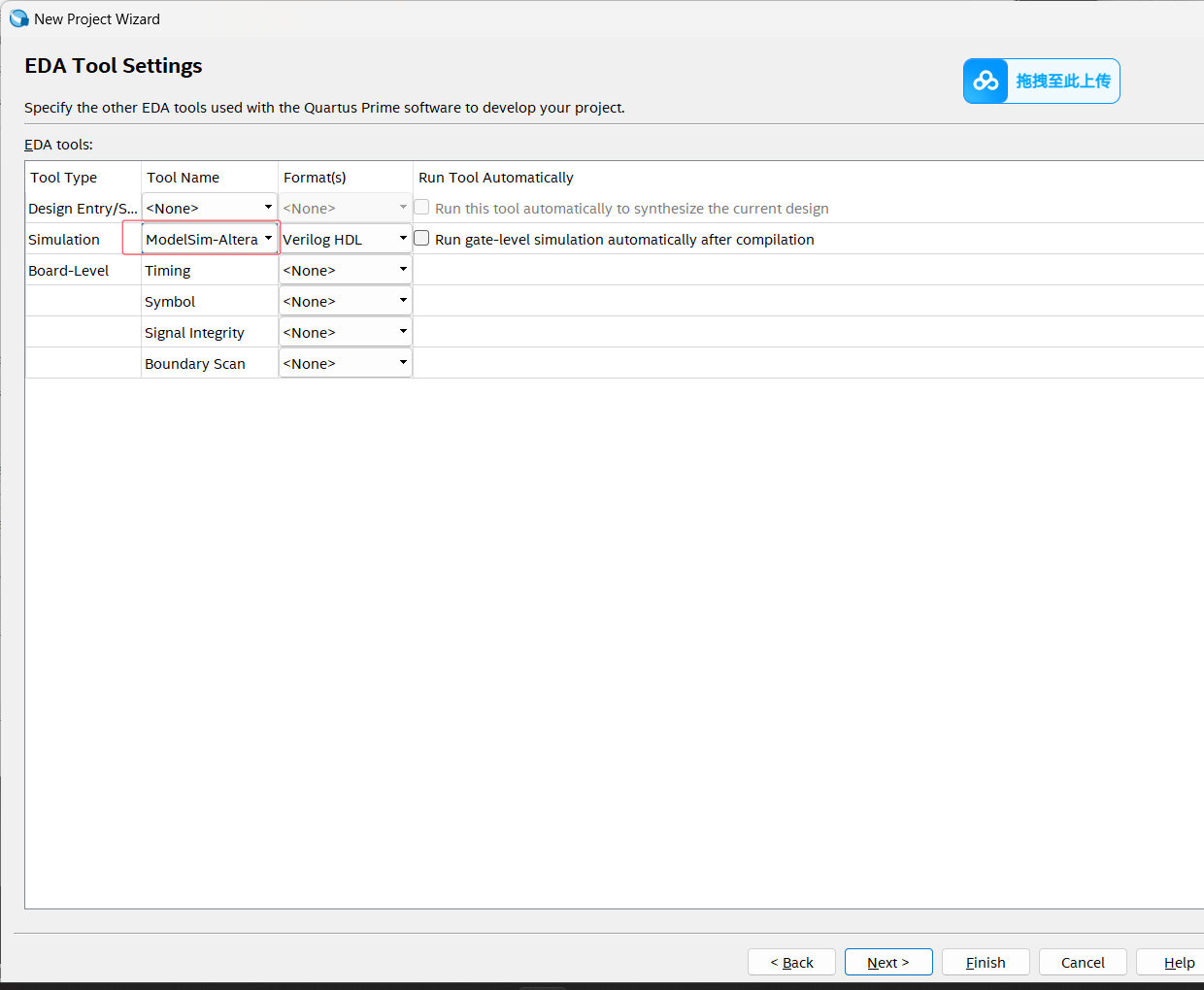

然后这里我们选择使用 ModelSim-Altera 进行仿真,然后我们直接点击下一步直接到结束即可

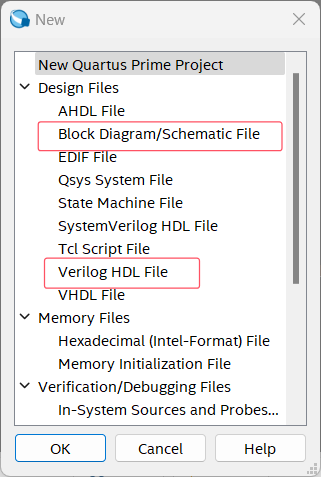

Block Diagram/Schematic File :绘制原理图需要使用的文件,后缀是 .bdf 和 .bsf

Verilog HDL File : 写 verilog 代码的文件类型,后缀是 .v

四位加法器

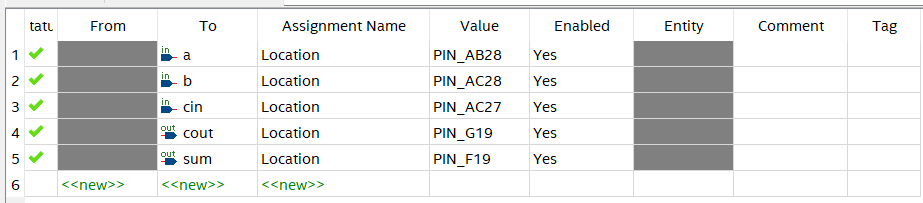

引脚的绑定:

实验现象:

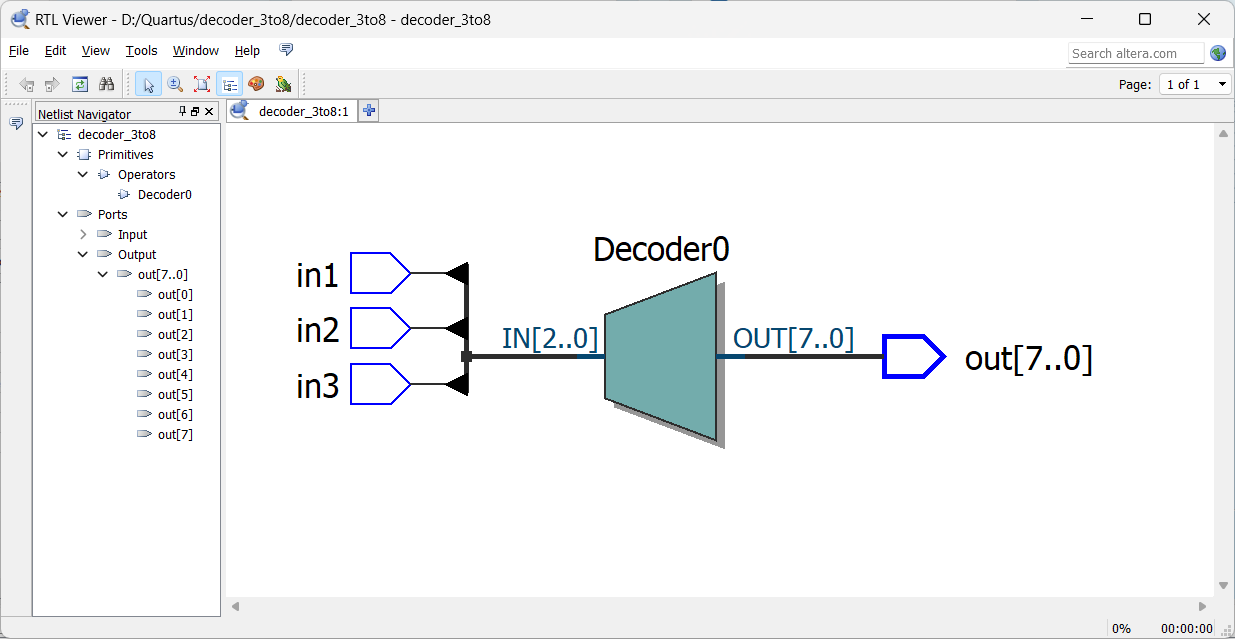

三八译码器及数码管显示

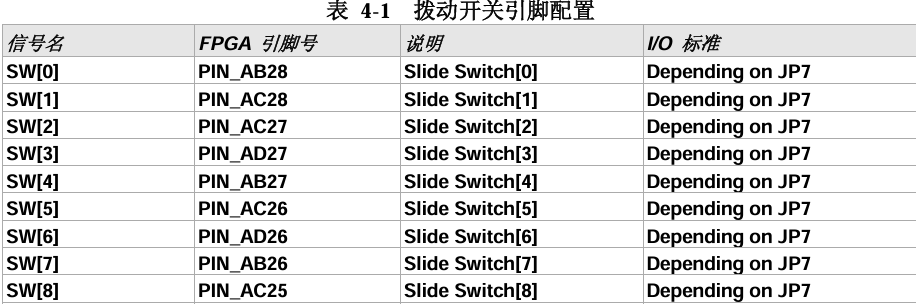

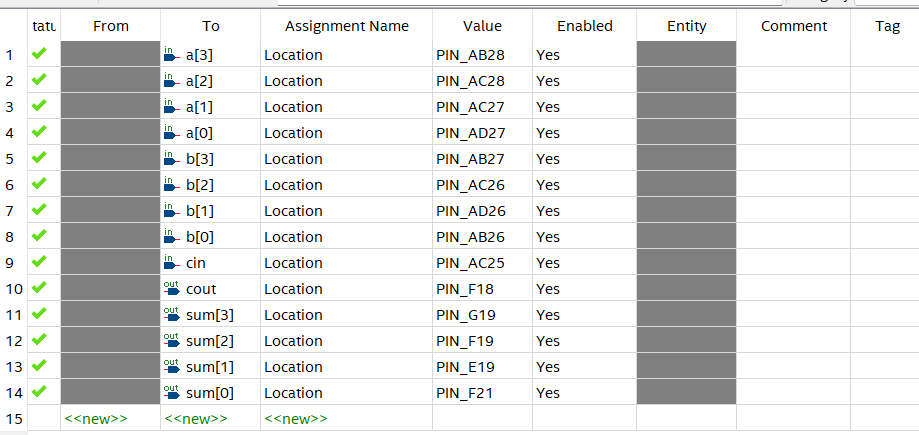

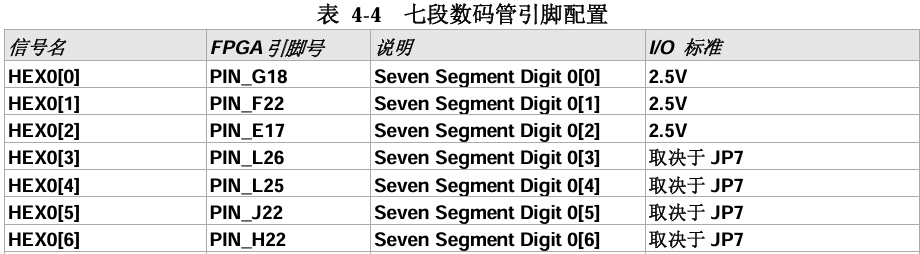

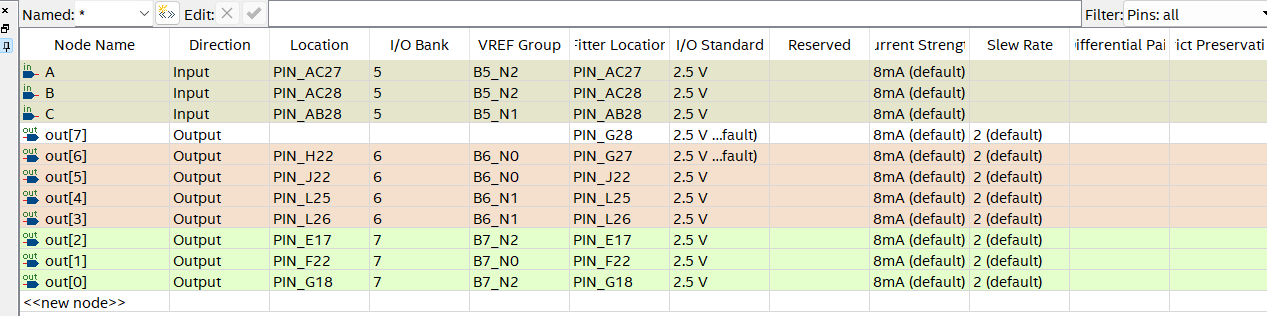

配置引脚

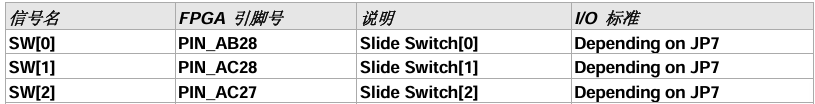

DE2-115 引脚列表:【整理】DE2-115引脚列表 word版-CSDN博客

使用3个SW作为输入信号,七段数码管作为输出显示

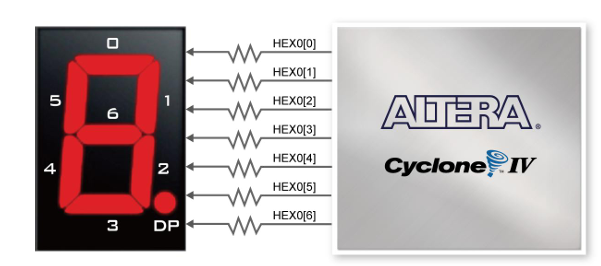

DE2-115配有八个七段数码管。它们被分成两组,每组四个,用来作为数字显示用。七段数码管的每个引脚(共阳模式)均连接到Cyclone IV E FPGA。FPGA输 出低电压的时候,对应的字码段点亮,反之则熄灭。 每个数码管的字段都从0到6依次编号,下图给出了它们的编号次序。

Cyclone IV E FPGA和七段段数码管间连接示意图如下:

要实现38译码器的结果在七段数码管上显示,需要满足逻辑如下表:

| 数码管显示数字 | 需要亮起来的小段 | 对应的八位二进制数 |

|---|---|---|

| 0 | HEX0[0]~[5] | 0000_0011 |

| 1 | HEX0[1]~[2] | 1001_1111 |

| 2 | HEX0[0],[1],[3],[4],[6] | 0010_0101 |

| 3 | HEX0[0],[1],[2],[3],[6] | 0000_1101 |

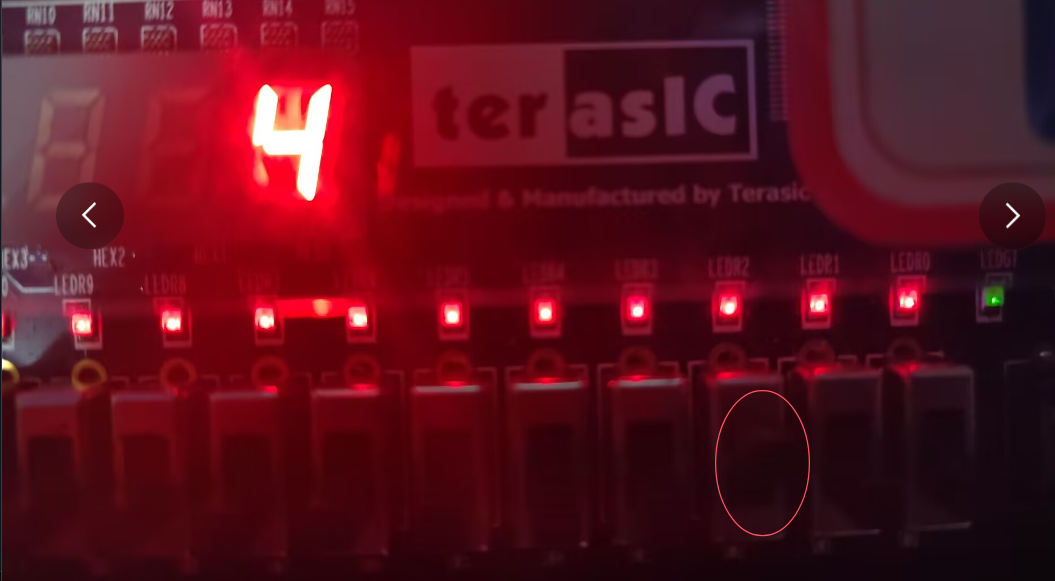

| 4 | HEX0[1].[2].[5],[6] | 1001_1001 |

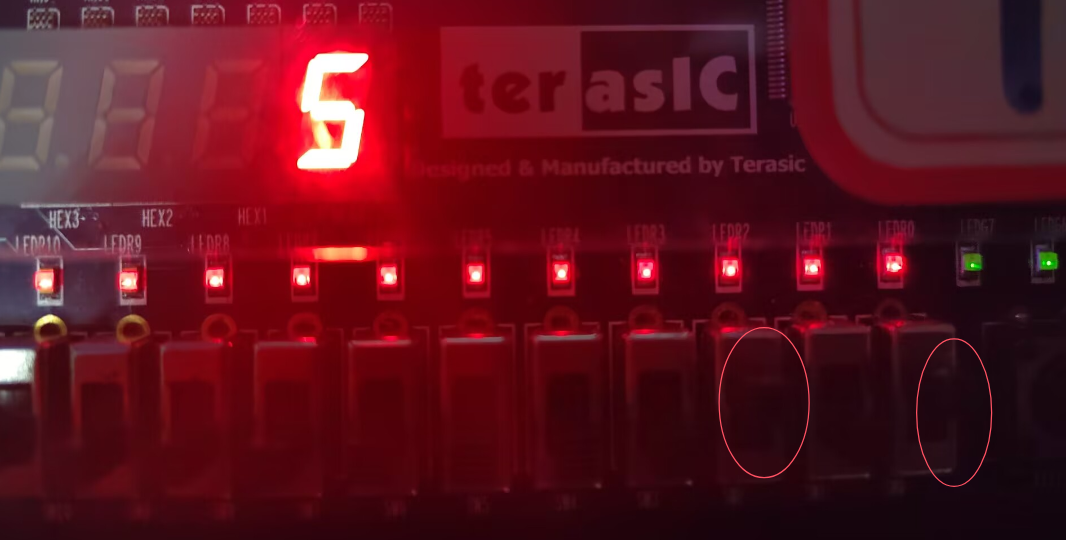

| 5 | HEX0,[0],[2],[3],[5],[6] | 0100_1001 |

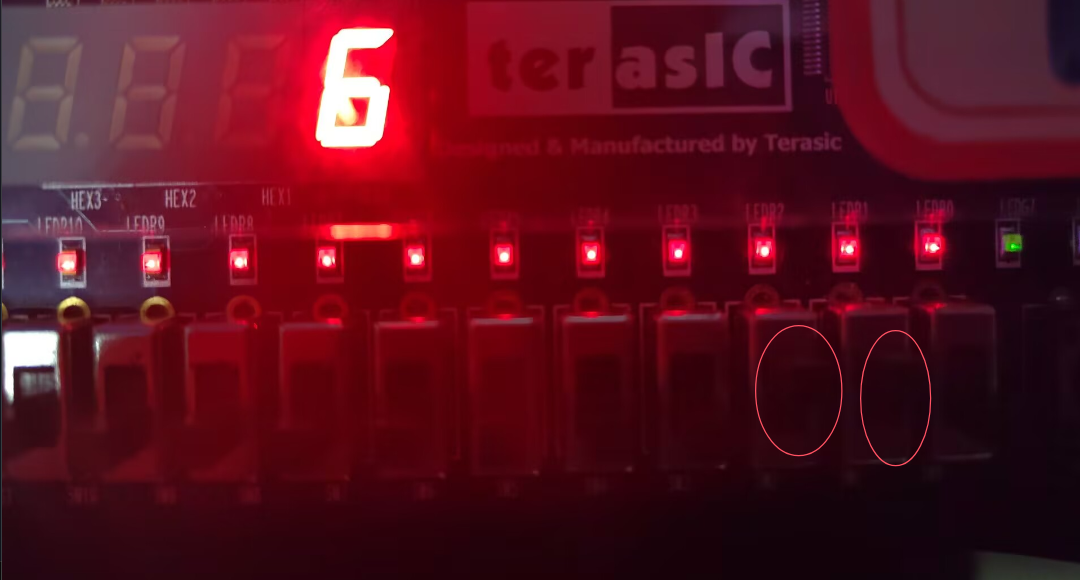

| 6 | HEX0[0],[2],[3],[4],[5],[6] | 0100_0001 |

| 7 | HEX0[1]~[3] | 0001_1111 |

module decoder_3to8

(input wire A , //输入信号1input wire B , //输入信号2input wire C , //输入信号3output reg [0:7] out //输出信号 out);

always@(*)case({A, B, C})3'b000 : out = 8'b0000_0011; 3'b001 : out = 8'b1001_1111;3'b010 : out = 8'b0010_0101;3'b011 : out = 8'b0000_1101; 3'b100 : out = 8'b1001_1001;3'b101 : out = 8'b0100_1001;3'b110 : out = 8'b0100_0001;3'b111 : out = 8'b0001_1111;endcaseendmodule

引脚绑定图如下:

因为38译码有八项输出,而译码器只有七个管脚,所以取out的前7项绑定为HEX0的七个管脚输出

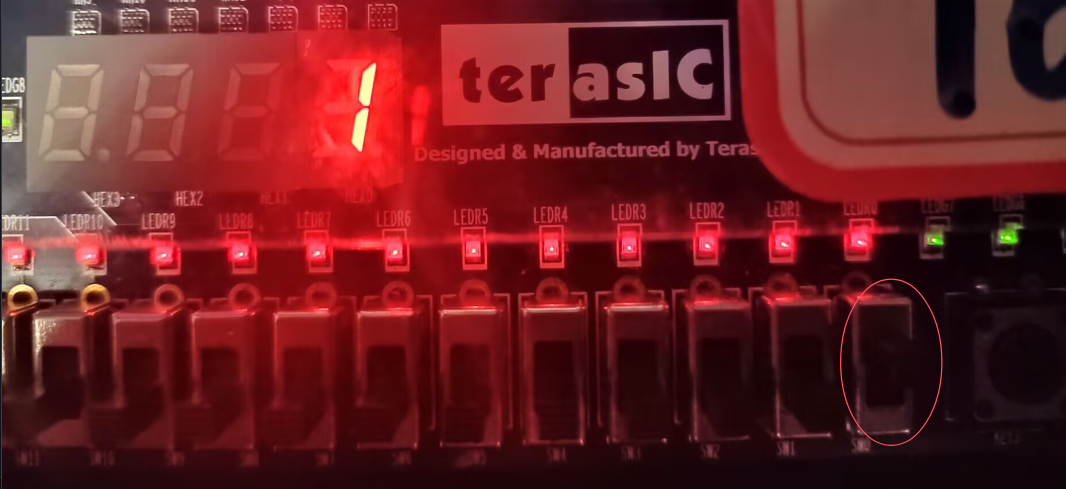

实验现象如下:

)