一.SystemVerilog介绍

1.SystemVerilog简介

SystemVerilog是一种用于设计和验证电子系统特别是集成电路的硬件描述语言(HDL)。它是由IEEE标准组织制定的,标准编号为IEEE 1800。SystemVerilog是Verilog语言的一个超集,它在Verilog的基础上增加了很多新特性,以支持更复杂的设计和验证任务。

2.SystemVerilog与Verilog的区别

面向对象编程(OOP):

- SystemVerilog:引入了面向对象编程的概念,包括类(class)、继承、封装和多态性,这使得设计和验证更加模块化和可重用。

- Verilog:不支持面向对象编程。

数据类型和变量声明:

- SystemVerilog:引入了更多的数据类型,如

logic,bit,byte,shortint等,并支持类型自动推导。 - Verilog:数据类型较为有限,主要包含整型、实型和位。

过程块和函数:

- SystemVerilog:引入了改进的

always块,如always_comb,always_ff,always_latch等,以及函数可以作为参数传递。 - Verilog:使用

always块描述时序逻辑,task和function定义过程和函数,但不支持函数作为参数传递。

断言和覆盖率:

- SystemVerilog:支持

assert语句和covergroup,用于验证设计的正确性和覆盖率。 - Verilog:不原生支持断言和覆盖率。

随机化和约束:

- SystemVerilog:支持随机化特性,可以用于生成测试向量。

- Verilog:不支持随机化和约束。

并发和同步:

- SystemVerilog:支持更高级的并发构造,如

fork和join,以及disable语句。 - Verilog:并发和同步的使用较为分离。

命名和作用域:

- SystemVerilog:引入了包(package)的概念和命名空间(namespace),提供了更好的作用域管理。

- Verilog:命名规则相对简单,作用域主要依赖于模块和端口。

模块化和接口: - SystemVerilog:支持参数化模块和接口,以及接口(interface)的使用,有助于模块间的连接和通信。

- 验证特性:

- SystemVerilog:提供了丰富的验证特性,如基于类的面向对象编程、动态数组、关联数组、队列、约束随机化等,这些特性在验证复杂系统时非常有用。

- 综合指导:

- SystemVerilog:在代码无法满足功能描述时,综合器将报错退出,避免非预期的行为。

二.实验准备

2.1创建项目

led_flow.sv:

module led_flow (input logic clk, // 时钟信号input logic rst_n, // 复位信号(低有效)output logic [7:0] led // 8位LED输出

);logic [23:0] counter; // 24位计数器,用于产生慢时钟信号// 计数器逻辑always_ff @(posedge clk or negedge rst_n) beginif (!rst_n)counter <= 24'd0;elsecounter <= counter + 1;end// LED流水灯逻辑always_ff @(posedge counter[23] or negedge rst_n) beginif (!rst_n)led <= 8'b0000_0001;elseled <= {led[6:0], led[7]};end

endmoduletestbench测试文件:

module led_flow_tb;logic clk;logic rst_n;logic [7:0] led;// 实例化待测试的流水灯模块led_flow uut (.clk(clk),.rst_n(rst_n),.led(led));// 时钟信号生成initial beginclk = 0;forever #10 clk = ~clk; // 50MHz时钟周期为20nsend// 测试逻辑initial begin// 初始化信号rst_n = 0;#100;rst_n = 1;// 仿真运行一段时间后结束#1000000;$stop;end

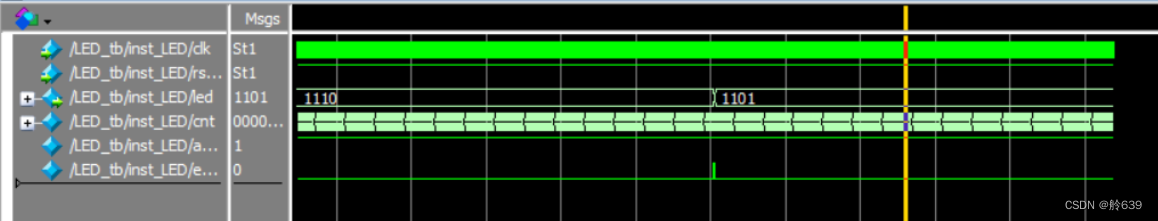

endmodule2.2 实验效果

2.3测试结果

正式发布:鸿蒙诞生以来最大升级,碰一碰、小艺圈选重磅上线)

——Docker将一台服务器的镜像移动到另外一台服务器)