6 FLASH 与 EEPROM 介绍

1. FLASH 介绍

在电路设计中,一般采用 FLASH 存储大容量的底层驱动程序或软件程序。例如,为 Pentium X86 系统架构存储配置信息的 BIOS 以及为 Power PC CPU 存储引导程序的 BOOT FLASH,采用的都是 FLASH 芯片。

目前常用的 FLASH 芯片有 NOR 和 NAND 两种规格。

NOR FLASH 于 1988 年诞生于 Intel 公司,而 1989 年,东芝公司开发出 NAND FLASH。

将 NAND FLASH 和 NOR FLASH 的区别列举如下:

(1)信号线区别:NOR FLASH 有独立的地址、数据引脚,与 SRAM 类似;而 NAND FLASH 的地址、数据引脚是复用的。

(2)读取方式:NOR FLASH 的应用特点是片上运行,即,由于其读取方便(地址、数据引脚分开),程序可直接在 FLASH 中运行,而无需导入 SDRAM 等高速存储器件,适于引导程序的存储。NAND FLASH 的应用特点是高密度大容量,适于大规模软件的存储,如上层应用软件的存储,但由于其地址、数据引脚复用在一起,操作时,需使用专门的驱动代码将读取指令转换为 NAND FLASH 可以识别的指令,读取操作复杂,运行时,需将软件程序导入 SDRAM 等器件后再执行。

(3)编程方式:NOR FLASH 的擦除和写入速度较慢,达到秒级;而 NAND FLASH 的擦除和写入速度快,仅为毫秒级;NOR FLASH 和 NAND FLASH 均可对片内某个块(Block)单独擦除,同时保留其他地址空间的存储内容,不过,NAND FLASH 的擦除单元块相对较小。

(4)存储容量:基于同样的价格,NAND FLASH 的容量更大。

【案例6】 热插拔导致单板 FLASH 损坏

某业务板的引导程序存储在主控板的 FLASH 中,在业务板插入机框并被主控板识别后,通过主控板上的 FLASH 完成其引导过程。业务板 CPU 和主控板 FLASH 之间的信号线通过背板相连。对业务板热插拔强度测试发现,有时,主控板上的 FLASH 被损坏。

【讨论】

业务板热插拔时,通过示波器测量主控板 FLASH 信号线的波形,发现信号过冲很大。FLASH 电源为 3.3V,而信号过冲达到了 5.6V。由于 FLASH 属 CMOS 器件,IO 接口电平超过电源电平时,将被门锁,严重时可能导致器件的损坏。

改板设计时,在 FLASH 信号线上串接 330 电阻,问题得到解决。

【拓展】

FLASH 是易损器件。除本案例提到的门锁问题外,设计中还需注意以下两个问题:

(1)ESD。调试和生产时,若不采取防静电措施,FLASH 器件极易遭到损坏,设计时,应尽量使 FLASH 远离单板边界。

(2)机械损坏。由于 FLASH 器件较薄,且横截面积相对较大,容易遭受机械损坏,设计时应注意 FLASH 器件不放在单板易弯曲处。

2. EEPROM 介绍

EEPROM 常用于单板信息(如单板名称、厂家名称、单板版本号、单板序列号等)的存储,高密度单板上的温度检测芯片内部也使用 EEPROM 存储温度阈值等信息。EEPROM 在应用上的特点是:容量小(SDRAM 的存储容量一般为几百兆至几吉比特位,FLASH 的存储容量一般为几百兆位,而 EEPROM 的存储容量一般仅为几千比特位)、非易失、读取方便(使用 I²C 总线)。

对 EEPROM 的应用重点应把握两点:寻址和 I²C 总线读写操作。以下就 ATMEL 公司的 AT24C 系列 EEPROM 器件,分别进行讨论。

1)寻址

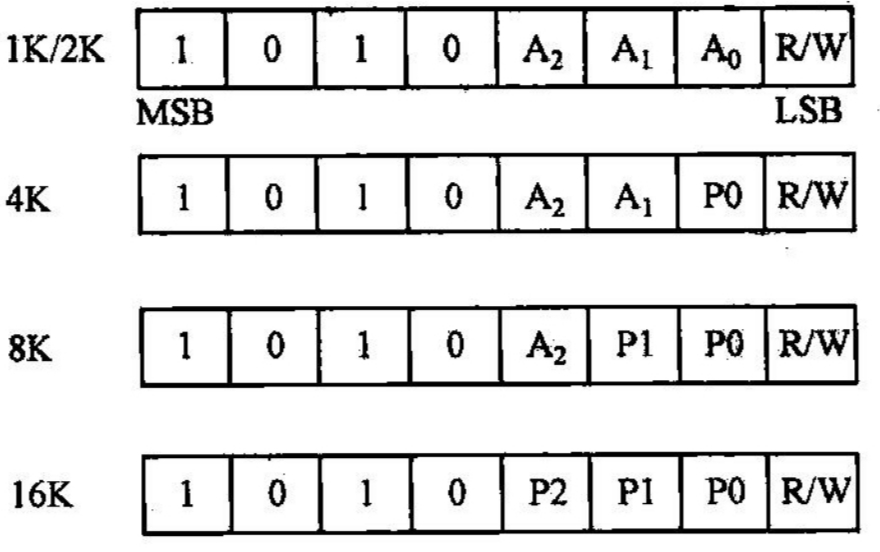

AT24C 系列 EEPROM 按存储容量分为五个型号:AT24C01、AT24C02、AT24C04、AT24C08、AT24C16,存储容量分别为 1Kbit、2Kbit、4Kbit、8Kbit、16Kbit。该系列器件提供三个地址引脚 A[2:0],寻址方式如下图所示。

AT24C 系列 EEPROM 利用八位地址位寻址,其中高四位(第 7~4 位)固定为“1010”,最末位(第 0 位)指示该操作是属于读或写。对 1Kbit、2Kbit 容量的型号,A[2:0] 引脚作为地址位的第 3~1 位,参与寻址。对 4Kbit 容量的型号,A[2:1] 引脚作为地址位的第 3~2 位,参与寻址。第 1 位由程序指定,用于选择器件内部的页地址。对 8Kbit 容量的型号,A[2:1] 引脚作为地址位的第 3 位,参与寻址,第 2~1 位由程序指定,用于选择器件内部的页地址。对 16Kbit 容量的型号,A[2:0] 引脚不参与地址,第 3~1 位由程序指定,用于选择器件内部的页地址(单片器件存储容量越大,页数越多)。

一条 I²C 总线上所连接的 EEPROM,必须拥有不同的地址。如下图所示,AT24C01、AT24C02 有三个地址引脚可用,因此,一条 I²C 总线上最多可挂八个器件,依次类推,对 AT24C16,由于无外部地址引脚可用,则一条 I²C 总线只能挂一个器件。

控制器(如 CPU)往往只提供一个 I²C 接口,而受地址引脚数目以及引脚容性负载的限制,一条 I²C 总线上所连接的 EEPROM 器件数目有限,为连接尽可能多的 EEPROM 器件,可以使用 I²C 接口扩展芯片,如 Philips 公司的 PCA9545 等。

2)I²C 总线操作

I²C(Inter-Integrated Circuit)总线是 Philips 公司开发的,由两根信号线(时钟 SCL、数据 SDA)组成的串行总线,用于控制器与外围设备之间的互连。通过 I²C 总线,控制器可以配置、读取外围设备的工作参数,总线上的每个设备都有唯一的地址标识(对使用 I²C 接口扩展芯片的情况,相当于使用了二级地址,头一级地址是 I²C 接口扩展芯片的地址,第二级地址才是待操作设备的地址),且每个设备都可作为发送器或接收器。

I²C 总线有如下特点:

(1)使用串行总线。采用两条信号线,即可将多个设备互连,PCB 设计时,走线应成菊花链。

(2)属于多主机总线。当总线上有两个以上的设备申请总线的主控权时,可通过仲裁决定最终的主控方。

(3)标准运行速率为 100Kbps,最高可达 1Mbps 以上。

(4)电源电压范围宽、功耗低。

(5)I²C 的信号线 SCL、SDA 属于 OD(Open Drain,漏极开路)电路,在电路设计上需做上拉处理。

以下以写操作为例,对 I²C 总线时序进行介绍。

为方便起见,下图中只列出 SDA 信号,而 I²C 操作中,SDA 信号需与 SCL 信号结合,才具有特定的意义。

各 I²C 操作之间以“起始位”和“停止位”作为间隔,如下图所示。当 SCL 处于高电平时,SDA 的下降沿表示起始位,上升沿表示停止位。

当 SCL 处于低电平时,SDA 的变化沿表示有效的地址或数据。

起始位之后,控制器发出待操作的从设备地址,以 A2:0=001 的 AT24C02 为例,SDA 信号线上的地址信息为 10100001,最末一个“0”表示此次操作为写。

接到控制器发出的设备地址后,作为从设备的 AT24C02 返回一个响应,即 ACK 位;接着,控制器发出待操作的从设备寄存器地址,发送完成,从设备再次返回一个 ACK 位。

最后,控制器发出需写入该寄存器的数据,发送完成,从设备同样返回一个 ACK 位。

最后由控制器发出停止位,本次操作完成。

例如,控制器向从设备地址为 0xA2,寄存器地址为 0x04 的寄存器写入数据 0x55,则 SDA 信号线上的数据依次为:起始位→0xA2→ACK 位→0x04→ACK 位→0x55→ACK 位→停止位。

由以上过程可知,在实质上,I²C 操作是一个主、从设备交互的过程。

I²C 总线能同时连接多个设备,当存在两个以上的设备同时申请,希望成为主设备时,需通过仲裁来决定谁能最终成为主设备。

I²C 总线仲裁的原理如下:

由于 SCL 和 SDA 信号均为漏极输出,当信号线被多个主设备驱动时,信号线最终的逻辑状态为这些主设备输出逻辑线与后的结果,即仅当所有的主设备都驱动信号线为高电平时,信号线才能表现为高电平逻辑,假如其中有一个主设备驱动输出低电平,则信号线表现为低电平逻辑。

I²C 总线的仲裁是在 SCL 高电平时,通过比较 SDA 的逻辑状态而完成的。

如下图所示,设备 1 和设备 2 在驱动 SDA 信号线的同时,在 SCL 处于高电平的时间段内,不断读取 SDA 信号线的状态,当发现 SDA 信号线的状态与自己的驱动逻辑状态不同,则停止对总线的控制。

【案例7】 读取百兆光模块信息出错

某传输产品光接口板上,光模块 SFP 的信息存储在 SFP 内部的 EEPROM 里,该信息可通过 CPLD 与 SFP 之间的 I²C 总线接口进行读取。在测试中,通过 CPLD 多次读取 SFP 的 EEPROM,偶尔会出现读取失败的现象。

【讨论】

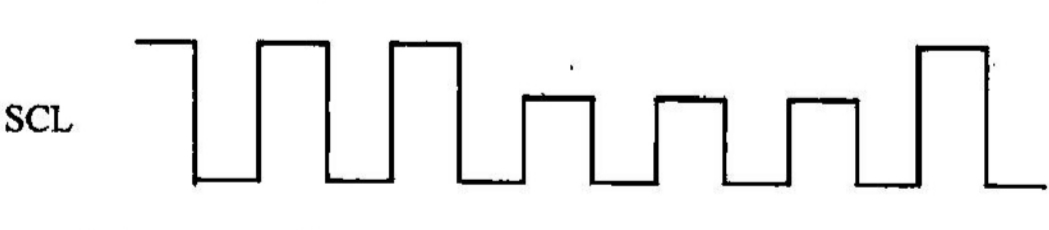

测试读取失败时 I²C 总线的波形,发现在 EEPROM 收到 CPLD 发出的地址信息后,时钟信号 SCL 的波形变为半电平状态,如下图所示。

I²C 规范提到,当 I²C 从设备在收到主设备的地址信息后,如果无法立即发起或响应传输,可通过将 SCL 拉低以将此情况通知主设备,主设备得知后,应等待一段时间,才能继续传输。

以上功能并没有实现在 CPLD 的代码中。在逻辑代码的设计里,SCL 将一直由 CPLD 驱动,以至于作为从设备的 EEPROM 驱动 SCL 为低电平后,作为主设备的 CPLD 仍然继续驱动 SCL 信号,导致 SCL 信号线上出现冲突,读取失败。

EEPROM 无法立即对传输作出响应的原因有两个:其一,I²C 时钟速率过高;其二,EEPROM 自身存在缺陷。在调试中,修改 CPLD 逻辑代码,一方面将 I²C 时钟速率由 400kHz 调整为 100kHz,另一方面在发出地址信息后,等待一段时间,再驱动 SCL 信号以继续数据的传输。修改后,问题得到解决。

理解要点:

① NOR FLASH 和 NAND FLASH 的区别。

② FLASH 一般用于存储大容量的底层驱动程序或软件程序,而 EEPROM 常用于单板信息等的存储。

③ 理解 EEPROM 的寻址方式,I²C 总线的操作方式等。

)