1 与存储器相关的经典案例

【案例1】时序裕量不足导致存储器测试出错

某单板CPU及其存储子系统由Freescale公司的MPC8260与Micron公司的某款SDRAM构成。在对SDRAM的高强度性能测试中,发现少量读写错误。

【讨论】

由于仅有少量读写出错,可判断原理图设计、配置寄存器的设置等均正确。测量SDRAM的电源纹波与噪声,符合要求。利用示波器的余辉功能测试数据信号的时序,如下图所示。

上图为MPC8260向SDRAM写数据时,在SDRAM一侧测试得到的波形。上方波形为数据信号DQ,下方波形为时钟信号CLK。时序测量参考点分别为CLK信号的1.5V位置和DQ信号的1.5V位置。

SDRAM器件资料对时序的要求为:建立时间Tsu>1.5ns,保持时间Th>0.8ns。结合测试结果,Tsu已远远满足要求,测得TH为1.4ns,即保持时间裕量TH_MARGIN为0.6ns,同样符合器件要求。

仔细查阅SDRAM器件资料上与时序相关的描述,发现在一段注释中提到:时序参考点为1.5V,但若输入信号的边沿速率小于1V/ns,时序参考点应改为VIL(max)或VIH(min)。注释中的“输入信号”包括时钟和数据信号,测得时钟信号CLK的10%~90%边沿速率为0.88V/ns,而数据信号DQ的10%~90%边沿速率为0.82V/ns,均小于1V/ns,因此时序参考点不能选在1.5V位置,而应选用VIL(max)和VIH(min)。SDRAM的CLK和DQ信号电平均为LVTTL,根据之前章节,V IL(max)=0.8V,VIH(min)=2V。时序测试方法如下图所示。

更正时序参考点后,数据信号DQ的保持时间TH为0.85ns,保持时间裕量TH_MARGIN仅为0.05ns。考虑到测量误差以及测试时间有限等因素,0.05ns的保持时间裕量不足以满足器件长时间正常工作的要求。在改板设计中,将时钟信号的走线长度缩短,以便增大数据信号的保持时间,时序测试波形图如下图所示。

【拓展】

存储器读写出错,需着重考虑以下几个方面:原理、电源、信号质量、时序、配置寄存器。

(1)原理:

其一,考查存储器控制器与存储器是否配对。在概要设计阶段,就应基于时钟频率、接口类型、存储容量、地址空间分配等完成对存储器的选型。

其二,原理图绘制中是否出现低级错误。下文将提到,不同种类的存储器,对线序的要求并不相同。例如,ZBT SRAM,数据信号和地址信号的线序可互换;又如SDRAM,DDR SDRAM、DDR2 SDRAM,数据信号的线序可任意互换,而地址信号的线序则不能互换。在SDRAM等的应用中,如地址信号线序未对齐,则无法实现对存储器的正确配置。

(2)电源:电源部分应着重考察电源平面是否完整,电源噪声和纹波是否超标。

(3)信号质量:ZBT SRAM、SDRAM、DDR SDRAM、DDR2 SDRAM等不同类型的存储器,对匹配电路的设计有不同的要求,只有匹配电路的元器件参数、放置位置等进行正确的选择和设计,才能保证信号质量。同时,由于存储器接口一般采用并行总线,在PCB设计时,应注意避免在相邻走线的信号之间产生串扰。

(4)时序:高速电路中的存储器接口设计,对时序分析的要求很高。存储器与系统性能密切相关,存储器运行速率的提高,有助于系统性能的提高,电路设计时,存储器接口属于高速接口,随着运行速率的提高,时钟周期不断减小,时序裕量也随之减小,时序设计时的难度越来越大。因此,在高速存储器接口设计中,应加强对信号线长度的控制,以满足器件的时序要求。

(5)配置模式寄存器:在SDRAM、DDR SDRAM、DDR2 SDRAM以及DDR3 SDRAM的应用中,存储器的许多特性需通过模式寄存器进行设置。若寄存器的值设置错误,存储器将无法正常工作。

以上就高速电路设计中存储器读写出错的五个潜在原因做了简要介绍,下文在具体介绍不同类型存储器时还将对此展开详细的讨论。

2 常用存储器介绍及其应用要点

2.1 存储器概述

电路设计离不开存储器件,对一个电路系统而言,一般包含以下几种存储器:EEPROM、FLASH、SDRAM(或DDR2 SDRAM、DDR3 SDRAM等),在高性能系统中,还包括ZBT SRAM(或DDR SRAM、QDR SRAM等)。其中,EEPROM一般用于存储单板信息(如单板名称、厂家名称、单板版本号、单板序列号等);FLASH用于存储底层驱动代码、软件代码等。SDRAM等用于大容量的缓存,ZBT SRAM等用于高吞吐率小容量的存储。

根据应用特性,将高速电路中常用的存储器分类如下图所示。

1. RAM

RAM(随机存储器,Random Access Memory)指存储内容可被快速地写入或读出,掉电后存储内容丢失的存储器。

RAM可分为SRAM(静态随机存储器,Static RAM)和DRAM(动态随机存储器,Dynamic RAM)两种。

1)SRAM

SRAM的优点是只要器件不掉电,存储内容就不丢失,无需刷新电路,工作速度快。缺点是集成度低、功耗大、价格高。SRAM的结构如下图所示。

上图是一种典型的SRAM结构,每个存储单元由六个MOS管组成,中间四个MOS管(Q2、Q3、Q3、Q3’)构成双稳态触发器,两侧的两个MOS管(Q1、Q1’)的开关状态由同一个选择信号CE控制。

数据写入时,数据信号D及其反相的信号D#分别出现在Q1和Q1’上,待选择信号CE将Q1和Q1’导通后,D和D#触发双稳态触发器,使之发生相应的翻转,并使翻转后的状态一直得到保持,直到下次数据写入事件发生。

数据读出时,选择信号CE有效并使Q1和Q1’导通后,A和A’点的逻辑状态出现在数据信号D和D#上,从而实现数据的读取,该读取的过程并不改变存储单元内双稳态触发器的状态。

每个SRAM存储单元由六个MOS管组成,功耗大、集成度低,但由于内部采用了双稳态触发器,也就无需不断地对内部存储的内容进行刷新。

SRAM可进一步分为ZBT SRAM、DDR SRAM、QDR SRAM等,将在后续章节中讨论。

2)DRAM

DRAM(动态随机存储器,Dynamic RAM)的优点是集成度高、功耗小、价格低。缺点是即便器件不掉电,存储内容也只能保持很短的时间,需不断地被刷新。典型的DRAM结构如下图所示。每个存储单元由一个MOS管及其寄生电容构成。由于数据信号的状态由电容的电荷量决定,因此每隔一段时间需对电容做一次充放电的刷新操作。

DRAM结构简单,功耗低、集成度高,但需要不断刷新内部存储的内容。

常用的DRAM可进一步分为SDRAM、DDR SDRAM、QDR SDRAM等。

2. ROM

ROM(只读存储器,Read Only Memory)指一旦写入,则无法擦除改写的存储器。此处,将ROM的定义做进一步的扩展,定义为非易失存储器,即器件掉电后,内部存储内容仍保留,且支持电可擦除可改写的只读存储器。

高速电路设计中常用的ROM包括EPROM(电可擦写可编程只读存储器)和FLASH(闪速存储器)。

理解要点:

SRAM和DRAM所各自具有的特性,是由各自不同的结构造成的。SRAM的特点是无需刷新,存储效率高,工作速度快,缺点是集成度低、功耗大、价格高;DRAM的特点是功耗低、集成度高,但需要不断地进行刷新。

2.2 SDRAM介绍及其应用要点

1. SDRAM概述

SDRAM指同步动态随机存储器。上文已介绍DRAM的特性及结构,SDRAM指同步的DRAM,同步指存储器的工作需要参考时钟。

SDRAM的信号电平为LVTTL,属单端信号。

对于同步存储器,有三个与工作速率相关的重要指标:内核工作频率、时钟频率、数据传输速率。就SDRAM而言,其内核工作频率、时钟频率和数据传输速率三者相同,最高速率可达200MHz,设计中常用的速率有100MHz、133MHz、167MHz。

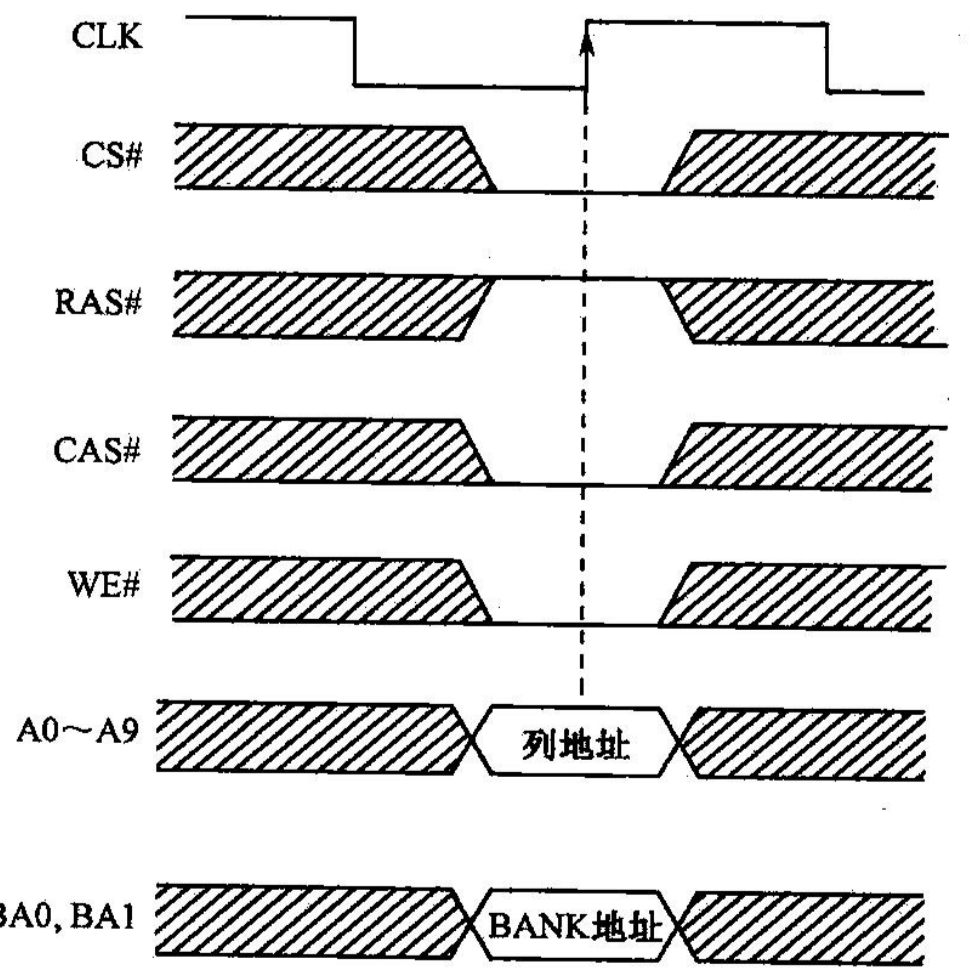

SDRAM的取址需通过三个步骤完成,如下图所示。

SDRAM存储空间被分为若干逻辑块(BANK),取址时,首先需提供BANK地址以找到待操作的逻辑块,然后需提供行地址和列地址以在该BANK内定位存储单元。因此,在器件资料上,SDRAM存储容量的

定义方式是:地址数×位宽×Bank(存储块)数。例如,Micron公司某款存储容量为512MB(512兆位)的SDRAM,有如下三种规格:

32M×4×4

16M×8×4

8M×16×4

规格1中,行地址信号线为A0~A12共十三根,可组成2^13个不同的行地址,列地址信号线为A0~A9、A11、A12共十二根,可组成2^12个不同的列地址,因此地址数为32M(2^25)。数据信号线为DQ0~DQ3共四根,因此数据线位数为4位。BANK信号线为BA0、BA1共两根,因此BANK数为4。

规格2中,行地址信号线为A0~A12共十三根,列地址信号线为A0~A9、A11共十一根,因此地址数为16M(2^24)。数据信号线为DQ0~DQ7共八根,因此位宽为8。与规格1相同,BANK数为4。

规格3中,行地址信号线为A0~A12共十三根,列地址信号线为A0~A9共十根,因此地址数为8M(2^23)。数据信号线为DQ0~DQ15共十六根,因此位宽为16。与规格1相同,BANK数为4。

以上三种规格的SDRAM,存储容量相同,差别仅在于引脚定义的略微不同,因此,封装相同。在设计中,原理图上做简单处理后,即可相互替换。

需补充说明的是,由于行地址选择和列地址选择处于SDRAM操作的不同阶段,因此行地址和列地址信号线可重复使用。

2. SDRAM芯片引脚介绍

以Micron公司容量为512MB(512兆位),规格为8M×16×4的某款SDRAM为例,介绍SDRAM的引脚定义。

(1)CLK:时钟信号,为输入信号。SDRAM所有输入信号的逻辑状态都需通过CLK的上升沿采样确定。

(2)CKE:时钟使能信号,为输入信号,高电平有效。CKE信号的用途有二个,其一是关闭时钟以进入省电模式,其二是进入自刷新(SELF REFRESH)状态。CKE无效时,SDRAM内部所有与输入相关的功能模块停止工作。在设计中需注意,应为CKE信号提供可靠的驱动源,如果在设计中无需CKE所提供的功能,应将CKE信号上拉为高电平。

(3)CS#:片选信号,为输入信号,低电平有效。仅当CS#信号有效后,SDRAM才能识别存储器控制器发送过来的命令。设计中,CS#信号应上拉。

(4)RAS#:行地址选通信号,为输入信号,低电平有效。

(5)CAS#:列地址选通信号,为输入信号,低电平有效。

(6)WE#:写使能信号,为输入信号,低电平有效。

(7)BA[1:0]:BANK地址信号,为输入信号。

(8)A[12:0]:行地址信号,为输入信号。

(9)DQ[15:0]:数据信号,为输入/输出双向信号。

(10)DQM[1:0]:数据掩码信号,为输入信号。当DQM有效时,数据线上出现的对应数据字节被接收器屏蔽。例如,当位宽为16位的SDRAM,数据总线分为两个字节,DQ[7:0]和DQ[15:8],DQML对应于DQ[7:0],DQMH对应于DQ[15:8],在读操作时,假设DQML为高电平而DQMH为低电平,则存储器控制器将忽略SDRAM发出的DQ[7:0],只存储DQ[15:8]信号线所携带的数据。DQM信号主要用于SDRAM的突发(Burst)操作,即一次连续发送若干字节的数据,当发送方不希望其中的某些字节被接收方接收时,可使用DQM信号以屏蔽这些字节。设计中需注意,若无需DQM所提供的功能,应将DQM下拉到GND。

(11)VDD:SDRAM内核工作电源,为3.3V。

(12)VDDQ:SDRAM数据总线I/O口电源,为3.3V。为VDDQ与VDD分开供电,有利于抗干扰,但为简化电路设计,一般还是采用同一个电源为VDDQ与VDD供电。

3. SDRAM的基本操作

如下表所示,SDRAM的基本操作方式有以下几种:空操作NOP、激活操作ACT、读操作READ、写操作WRITE、预充电操作PRECHARGE、自刷新操作SELF REFRESH、配置寄存器操作LOAD MODE REG等。各操作方式是通过CS#、RAS#、CAS#和WE#这几根信号线的各种状态组合而选择的。

表中,H代表逻辑高电平,L代表逻辑低电平,X代表与该信号的逻辑状态无关。以下对几个常用的操作进行详细介绍。

1)ACT(激活操作)

前文提到,对SDRAM存储单元的取出需提供三个参数:BANK地址、行地址、列地址。ACT操作执行时,存储器控制器发出其中的两个地址:BANK地址(利用BA[1:0]信号)、行地址(利用A[12:0]信号),以便激活待操作的“行”。第二个参数,即列地址,将在READ或WRITE操作中指定,即,ACT操作的目的是发出待操作的BANK地址及行地址,因此片选信号CS#和行选通信号RAS#需有效,而列选通信号CAS#和写使能信号WE#需保持为无效。如下图所示,ACT操作时,CLK信号上升沿采样到的关键信号逻辑状态分别为:CS#低电平有效,RAS#低电平有效,CAS#高电平无效,WE#高电平无效。采样地址总线得到行地址、采样RAS#[1:0]信号线得到BANK地址。

2)READ(读操作)

存储器控制器利用READ操作发出读指令,同时发出两个地址:BANK地址(利用BA[1:0]信号)、列地址(利用A[9:0]信号),即,READ操作的目的有两个,其一是发出读命令,这通过有效片选信号CS#、有效列选通信号CAS#、无效行选通信号RAS#以及无效写使能信号WE#实现;其二是在地址总线上发出列地址。如下图所示,READ操作时,CLK信号上升沿采样到的关键信号逻辑状态分别为CS#低电平有效、RAS#高电平无效、CAS#低电平有效、WE#高电平无效。采样地址总线得到列地址,采样BA[1:0]信号线得到BANK地址。

数据的读操作,涉及以下几个短时参数:

(1)tRCD(RAS到CAS延迟),即RAS#信号有效后到CAS#信号有效,这之间的延时。在ACT命令选定行操作的行之后,需延时tRCD,才能切换到列的选择。因此ACT命令(完成行选择)与READ指令(完成列选择)之间的延时为t\({\text{RCD}}\)。

(2)CL(CAS Latency),即CAS潜伏期参数。READ指令发出后,存储器根据采样得到的行地址和列地址,将对应存储单元的数据放大,以便传输到数据总线上,这个过程所消耗的延时称为CL。因此,从READ指令发出到数据总线上出现第一个数据,这之间的延时定义为CL。

(3)tRAS:指ACT指令到PRECHARGE指令的延时。PRECHARGE指令所对应的操作将在下文讨论。

(4)tRC:指两次ACT指令之间的时间间隔。

(5)tRP:指PRECHARGE指令到下一次ACT指令的延时。

以上参数与SDRAM的存储性能密切相关,一般而言,延时参数值越小,存储器的存储性能越高,如下图所示为数据读取时序图。

在SDRAM器件资料中,以上参数都以时钟周期为单位,如某SDRAM的CL参数为2.5,假定其工作时钟频率为100MHz,则该器件的CAS潜伏期为25ns。

对读操作而言,从ACT命令开始,到第一个数据出现在总线上,延时为tRCD+CL。

3)WRITE(写操作)

WRITE操作与READ操作类似,不同点在于WRITE操作时,需有效WE#信号。如下图所示,WRITE操作时,CLK信号上升沿采样到的关键信号逻辑状态分别为:CS#低电平有效、RAS#高电平无效、CAS#低电平有效、WE#低电平有效。采样地址总线得到列地址、采样BA[1:0]信号线得到BANK地址。

数据写操作的流程图如下图所示。

数据写入时,同样需满足tRCD、tCAS、tRC、tRP等参数的要求,与读操作不同的是,写操作不涉及CL参数,但增加了tWR参数。tWR(Write Recovery Time,写回时间)是指SDRAM将数据总线上符号入的数据导入内部存储单元所需要的时间。

对写操作而言,从ACT命令开始,到第一个数据被写入,延时为tRCD。

4)BURST(突发操作)

在应用中,存储器的一次数据传输通常涉及多个字节,例如,某些CPU的存储接口数据总线为64位,则一次传输涉及8字节数据。通常,这8字节数据在存储器中处于相邻的位置。因此,采用BURST操作,可简化读写命令。BURST操作,即一次读写命令可传输同一行中若干连续的存储单元,一次传输字节的数量称为突发长度(Burst Length)。

下图是突发长度为4的BURST操作示例。在发出读命令的同时,地址总线上提供第一个存储单元的列地址n,此后SDRAM连续地在数据总线上发出同一行(行地址在前面的ACT操作中给出)中,列地址为n、n+1、n+2、n+3这四个相邻存储单元的数据。

单纯就BURST操作来看,相对于非BURST操作,BURST操作本身并不能提高传输性能,但BURST操作有利于简化SDRAM的读写命令,有利于系统整体性能的提升。如下图所示,某CPU连续发出四个读命令(非BURST操作),从SDRAM中读取四个存储单元的数据,与BURST操作相比,所消耗的时钟周期相同。但在BURST操作中,CPU发出第一个读命令后,其余时间处于空闲,而在非BURST操作中,CPU需连续发出四个读命令,耗费了宝贵的CPU资源。因此不利于系统的整体性能的提升。

SDRAM的读命令都是采用BURST操作,任何命令可被配置为BURST或非BURST操作。若被配置为BURST操作,还需设置突发长度,可选的长度有1、2、4、8,突发长度设置为1时,其等效于非BURST操作。

5)PRECHARGE(预充电操作)

对SDRAM内部某一行的操作完成后,如需继续对另一行进行操作,应先关闭当前的工作行,该操作称为PRECHARGE(预充电)操作。SDRAM存储单元依靠电容充放电实现存储单元逻辑状态的记录,因此在完成一次操作后,需对已操作行逻辑的行进行回写。

PRECHARGE操作时,CLK信号上升沿采样到的关键信号逻辑状态分别为:CS#低电平有效、RAS#高电平无效、CAS#高电平无效、WE#低电平有效。

当PRECHARGE操作中,引脚A10用于选择某一Bank还是所有Bank同时被预充电。当A10为高电平时,所有的Bank同时被充电;当A10为低电平时,由BA[1:0]指定预充电的Bank地址。由于预充电操作需要一定的时间,在发出预充电操作的命令后,需等待tRP时间才能发起另一行的操作(即从PRECHARGE命令到另一行的ACT之间的时间间隔需满足参数tRP。如下图所示,PRECHARGE命令(CS#低电平有效、RAS#低电平有效、CAS#高电平无效、WE#低电平有效)发出后,需等待t\({\text{RP}}\)时间,才能对另一行发出ACT操作,而在读操作时间内,本次数据的传输仍继续进行。

以下分析PRECHARGE对存储性能的影响。对于读操作后的PRECHARGE操作,在发出PRECHARGE命令及其以后的tRP时间段内,数据传输仍可继续进行,因此存储性能不受影响。而对于写操作,根据数据写时序图,在总线上出现最后一个数据后,还需延时tWR才能发出PRECHARGE命令,因此在写操作时,存储性能将受到PRECHARGE操作的影响。

6)AUTO PRECHARGE(自动预充电操作)

PRECHARGE操作,要求存储器控制器主动发出PRECHARGE命令,占用了宝贵的控制器资源。而AUTO PRECHARGE操作则无需外部控制器的指令即可自动地实现PRECHARGE功能。

AUTO PRECHARGE操作通过在读或写命令发出时信号线A10的状态来决定,本次读或写操作完成后,是否对本次操作所涉及的行自动执行PRECHARGE,如下图所示。需注意,对于AUTO PRECHARGE,仍需满足参数tRP的要求。

7)AUTO REFRESH(自动刷新操作)

根据组成结构可知,SDRAM需不断刷新才能保持内部存储的数据信息,刷新操作由AUTO REFRESH指令发起。AUTO REFRESH操作时,CLK信号上升沿采样到的关键信号逻辑状态分别为:CS#低电平有效、RAS#低电平有效、CAS#低电平有效、WE#高电平无效。

在发起AUTO REFRESH操作之前,要求对当前工作的行执行PRECHARGE操作,并等待tRP的延时满足后才能执行AUTO REFRESH。

SDRAM存储单元能可靠保存数据的时间约为64ms,因此设定每个存储单元的刷新周期是64ms。SDRAM每次针对一行进行刷新,以8192行的SDRAM为例,刷新操作应每7.8125us执行一次,由于刷新操作是SDRAM自身的行为,与外部存储器控制器无关,因此刷新操作的地址并不会出现在地址总线上。

刷新操作的时间用参数tRFC定义,该参数的值较大,以工作时钟频率为133MHz的SDRAM为例,刷新操作最少需消耗9个时钟周期,在此期间,SDRAM不响应任何外部命令。由此可知,刷新操作是影响SDRAM性能的最主要因素。SRAM的内部无需刷新操作,从这一点来看,SRAM的存储性能远高于SDRAM。

刷新操作与预充电操作的实现机制类似,二者的不同点有:其一,预充电需伴随读写操作,属随机性的操作,而刷新操作是定期性的操作;其二,一次完整的刷新操作包括对所有行的操作,而一次预充电操作可以针对某一特定的BANK。

8)SELF REFRESH(自刷新操作)

从省电角度考虑,当无流量负荷时,应通过无效CKE信号以使SDRAM进入休眠状态。但进入休眠状态后,仍需不断刷新SDRAM以保存其内部存储的数据,SELF REFRESH操作与AUTO REFRESH类似,唯一不同的是前者针对的是休眠状态的SDRAM(即CKE信号无效)。

9)上电初始化

SDRAM要求V\({DD}\)和V\({DDQ}\)同时上电,且在输入时钟CLK稳定后,等待至少100μs后才能开始如下的初始化流程:

① 通过PRECHARGE操作对所有BANK预充电。

② 发起数次AUTO REFRESH操作,至少要求两次。

③ 配置模式寄存器。

④ 开始正常工作。

10)模式寄存器的配置

在上电初始化的步骤中,配置模式寄存器是关键的一步。模式寄存器用于定义SDRAM的操作模式,如BURST模式、CL参数、突发长度等,模式寄存器的值与SDRAM的正常工作密切相关。

配置模式寄存器时,CLK信号上升沿采样到的关键信号逻辑状态分别为CS#低电平有效、RAS#低电平有效、CAS#低电平有效、WE#低电平有效,地址总线输出模式寄存器的值。此处,需注意的是,模式寄存器的值是通过地址总线,而不是数据线发出。正是这个原因,在SDRAM(包括后续章节将要介绍的DDR SDRAM和DDR2 SDRAM)的设计中,地址总线的线序不能任意交换。由于SRAM的工作不涉及模式寄存器的配置,因此其地址总线线序是可以任意交换的。如图下图所示为模式寄存器的配置图。

模式寄存器的第12~10位为保留位;

第9位为WB,指写突发模式(Write Burst Mode)。SDRAM的读命令都采用突发模式,而对写命令是否采用突发模式,则可通过模式寄存器的WB位进行设置,当WB位被设置为0时,写命令将采用突发模式(Burst),否则采用非突发模式。

第8~7位为Op Mode,一般设置为[00],表示采用标准的配置方式。

第6~4位为CAS Latency,即CAS潜伏期参数,[001]表示CL=2,[010]表示CL=3。CL表示从读命令发出到第一个数据出现在总线上的时间,因此CL越小越有助于提高存储效率,但CL值设置得太小,却不利于SDRAM工作速率的提高。例如,某款SDRAM,当CL设置为2,工作速率最高可达100MHz,而CL设置为3时,最高速率可达133MHz。

第3位为BT,指突发类型(Burst Type)。该位确定突发操作时连续传输字节的顺序。

第2~0位为Burst Length,指突发长度(1000]表示突发长度为1,等同于非突发操作;[001]表示突发长度为2;[010]表示突发长度为4;[011]表示突发长度为8。

5. SDRAM 时序参数

高速设计中,时序设计是重要的一环。存储器应用以及调试中的许多问题都与时序设计有关。对时序设计的详细内容,请参考之前章节,本小节仅就SDRAM应用中,需重点关注的时序参数进行介绍。

前文介绍的tRCD、CL、tRAS、tRC、tRP、tWR等时间参数,是SDRAM自身的特性参数,用于对存储性能的分析和比较,但不属于时序分析的参数。

SDRAM与时序以及信号质量相关的重要参数有以下几个:

(1)tAH:地址信号保持时间和建立时间要求。

(2)tDH、tDS:数据信号保持时间和建立时间要求,控制信号包括CS#、RAS#、CAS#、WE#、DQM等。

(3)tOH:时钟信号高电平和低电平的最小脉宽,这是一个与信号质量相关的要求,高电平脉宽指信号在1.5V(LVTTL中的高电平)之上的宽度,低电平脉宽指信号在1.5V(LVTTL中的低电平)之下的宽度,需注意,当时钟信号边沿速率小于1V/ns时,高电平脉宽和低电平脉宽不再等于1.5V,而是参考VIH(min);对LVTTL电平,VIH(min)=2V,VIL(max)=0.8V。

(4)tOH:数据输出保持时间。

5. SDRAM 测试方法

下文所列列举的测试方法不仅适用于SDRAM,同时还适用于DDR SDRAM、DDR2 SDRAM等,因此用“存储器”指代这些类型的DRAM。

单板设计完成后,存储器接口的测试作为重要的调试项。如下图所示为针对存储器接口的高强度流量测试,一般采用两种方法对存储器接口进行测试。

1)对存储器接口的高强度流量测试

为产生高强度流量,一般有两种途径。

途径一,单板正常工作,通过编制特定的码流,使尽量多的数据在存储器控制器和存储器之间传输。例如,某以太网交换机项目,正常的数据流只需通过交换芯片转发即可,无需送到CPU。CPU仅负责错误数据以及配置数据等数据流的处理。为测试与CPU接口的SDRAM,可通过BIST测试等流量发生器以高速发送配置数据流,以提高CPU与SDRAM之间数据接口的流量负荷,经长时间高低温的测试,可实现对SDRAM接口的验证。

途径二,某些存储器控制器芯片带有BIST(内建测试,Build In Test)功能,通过设置控制器的内部寄存器,即可触发控制器对外部存储器的高速测试。BIST是一种DFT(可测试性设计,Design For Testability)技术。由于其测试速率高、测试种类多、对信号路径的测试覆盖率高、测试时间短、测试可靠性好,是一种很好的存储器测试方法。

2)利用示波器对存储器接口信号线测试

存储器的信号分为两种:单向信号如控制信号、地址信号;双向信号如数据信号。

对于单向信号,发送方为存储器控制器,接收方为存储器;而对于双向信号,写操作时,发送方为存储器控制器,接收方为存储器,读操作时,发送方为存储器,接收方为存储器控制器。

对单向信号的时序测试,测试点选取在存储器一侧即可。

对双向信号的时序测试,可通过对存储器控制器(如CPU等)编程,使控制器主动读或写存储器,从而在存储器接口上产生一定的数据流,以便进行信号测试。该方法的优点在于,通过程序的编写,可分别对读操作和写操作进行单独的测试,缺点在于产生的流量负荷相对较低。

此处需简要叙述在双向信号测试中,将读和写操作区分开来的意义。利用示波器测试信号质量或时序,都应在接收端进行,而存储器的数据信号属于双向信号,当读写操作混杂时,难以辨别所测得的信号是发送端波形还是接收端波形,而将读写操作区分开来后,读操作时,存储器控制器为接收方,因此发送端测得的数据信号波形都属于接收端波形,可直接用于信号质量和时序分析,同理写操作时测量应在存储器一侧进行。

在故障诊断时,往往需要基于正常工作时的流量对存储器进行信号测试,而正常工作时读、写操作是混杂在一起的,在这种情况下,可采用以下的方法区分读、写操作。

示波器有四个输入通道,即一次最多可测量四个信号。SDRAM属于同步DRAM,即数据信号DQ的时序需参考时钟信号CLK。因此,CLK和DQ需占用两个通道,剩下的两个通道可用于只读、写操作。

根据表7.1,读操作区别于其他操作的特征可取为:CAS#为低电平,RAS#为高电平。需说明的是,该特征同样适用于AUTO REFRESH和SELF REFRESH操作。在REFRESH操作时,数据信号线上不会发生状态的翻转,因此不会影响数据信号时序的测量。如下图所示,利用CAS#和WE#组成的特征模式触发操作,需注意,读操作时,CAS#低电平有效后,需等待一个CL延时(CL=2),才能捕捉到数据信号DQ。

同理,写操作区别于其他操作的特征为:CAS#为低电平,WE#为低电平,下图所示。该特征同样适用于模式寄存器的配置操作,但配置模式寄存器只是在上电初始化时发生一次,不会影响数据信号时序的测量。

以上的时序测试需用到示波器的Pattern(模式)触发方法。如下图所示截取自Tektronix公司DPO7104示波器的Pattern触发选项页。

• 在Trigger Type(触发类型)处选择Pattern。

• 在Pattern Type(模式类型)处选择AND(与逻辑)。

• 在Input Threshold(输入门限阈值)处,设定各个通道的触发条件及逻辑电平阈值,如写操作,Ch1(通道1)为CLK,Ch2为CAS#,Ch3为WE#,Ch4为DQ,则可设定触发条件为Ch2和Ch3为逻辑0,用“L”表示,不要求Ch1和Ch4的逻辑状态,用“X”表示,逻辑阈值设置为LVTTL的中间电平1.5V。

理解要点:

① SDRAM的性能由三个指标相关:内核工作频率、时钟频率、数据传输速率。

② SDRAM的基本操作及相关控制信号的电平状态。

③ SDRAM的时序参数、时序参数的理解。

④ 利用示波器进行SDRAM的信号完整性、时序测试方法。

)