芯片选择

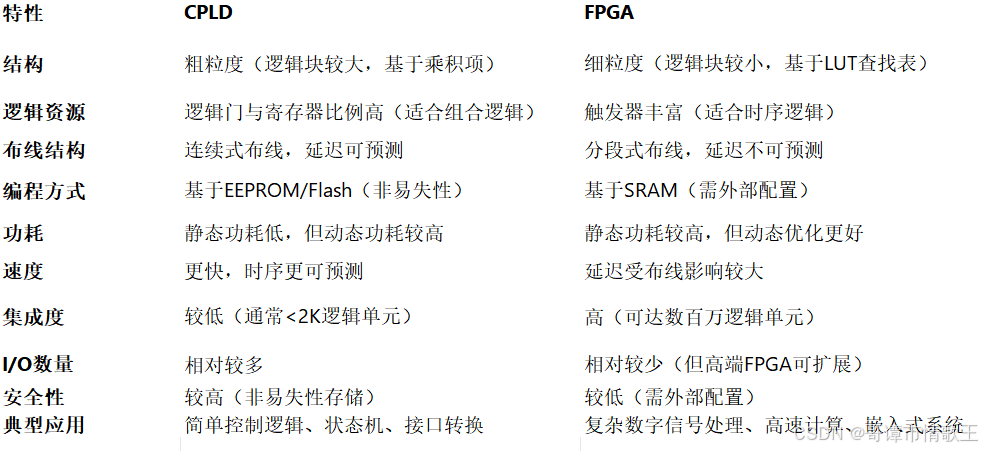

为什么选用FPGA而不用CPLD进行练习,将两者的主要技术进行比较

显而易见,

CPLD 适合组合逻辑和确定性时序应用,如地址译码、总线控制、简单状态机,其非易失性特性使其适合上电即运行的场景。

FPGA 适合时序逻辑和大规模并行计算,如DSP、AI加速、高速通信,其可重构性使其适合原型开发和动态调整。

所以进行开发练习采用FPGA更为优势。

实战练习

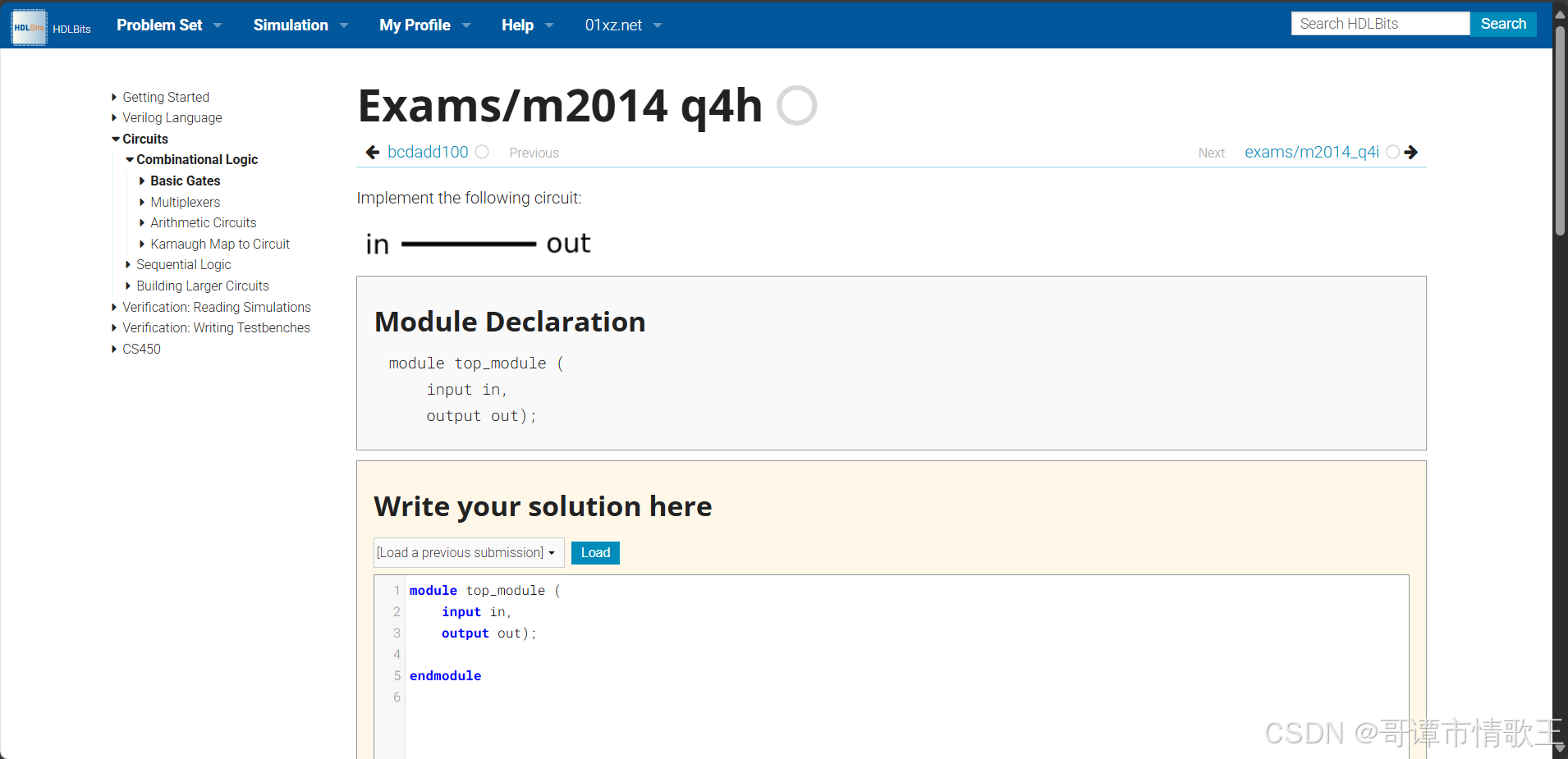

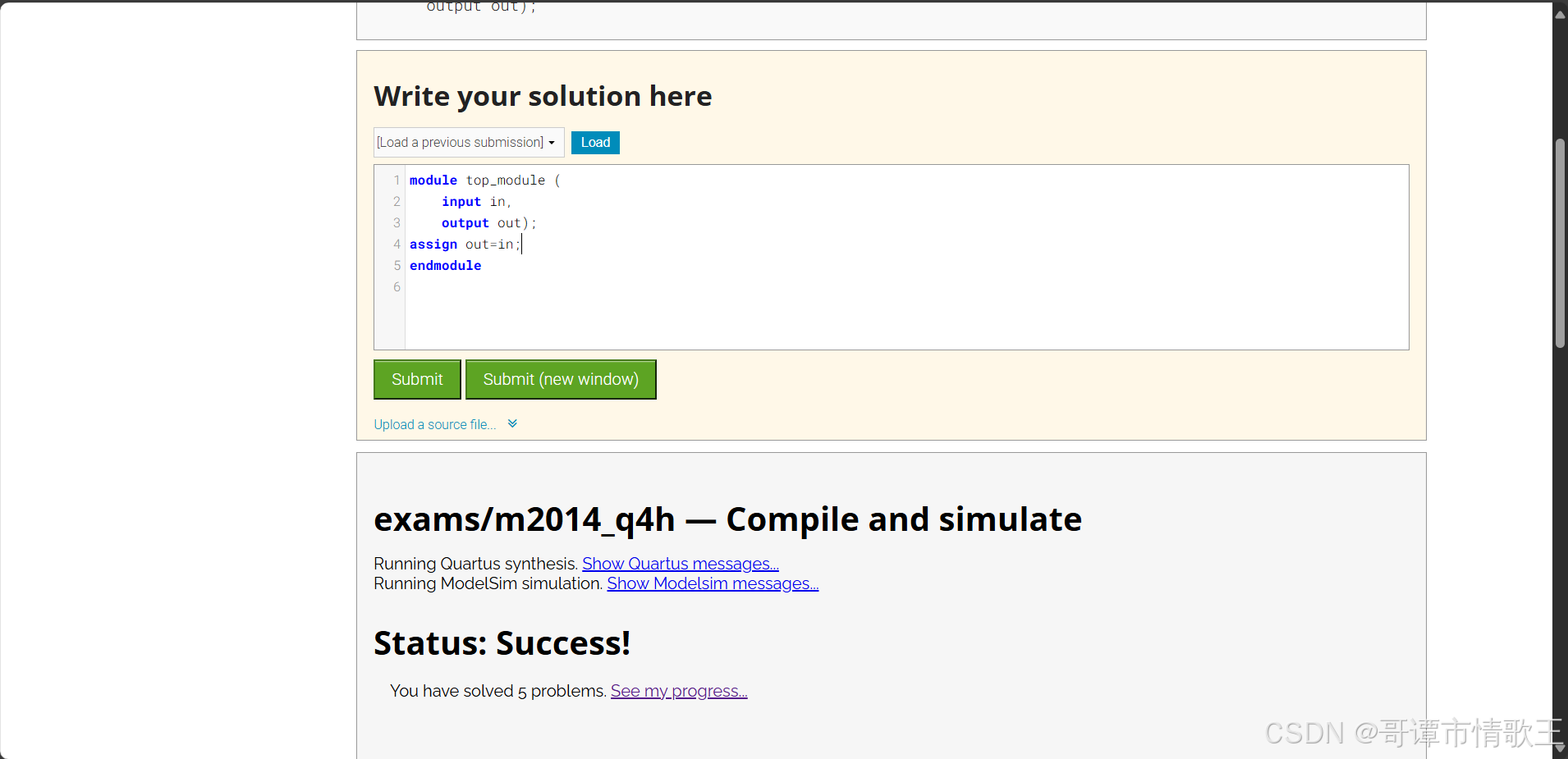

接下来我们去HDLBits官网上找几个组合逻辑的题目实践一下

Wire

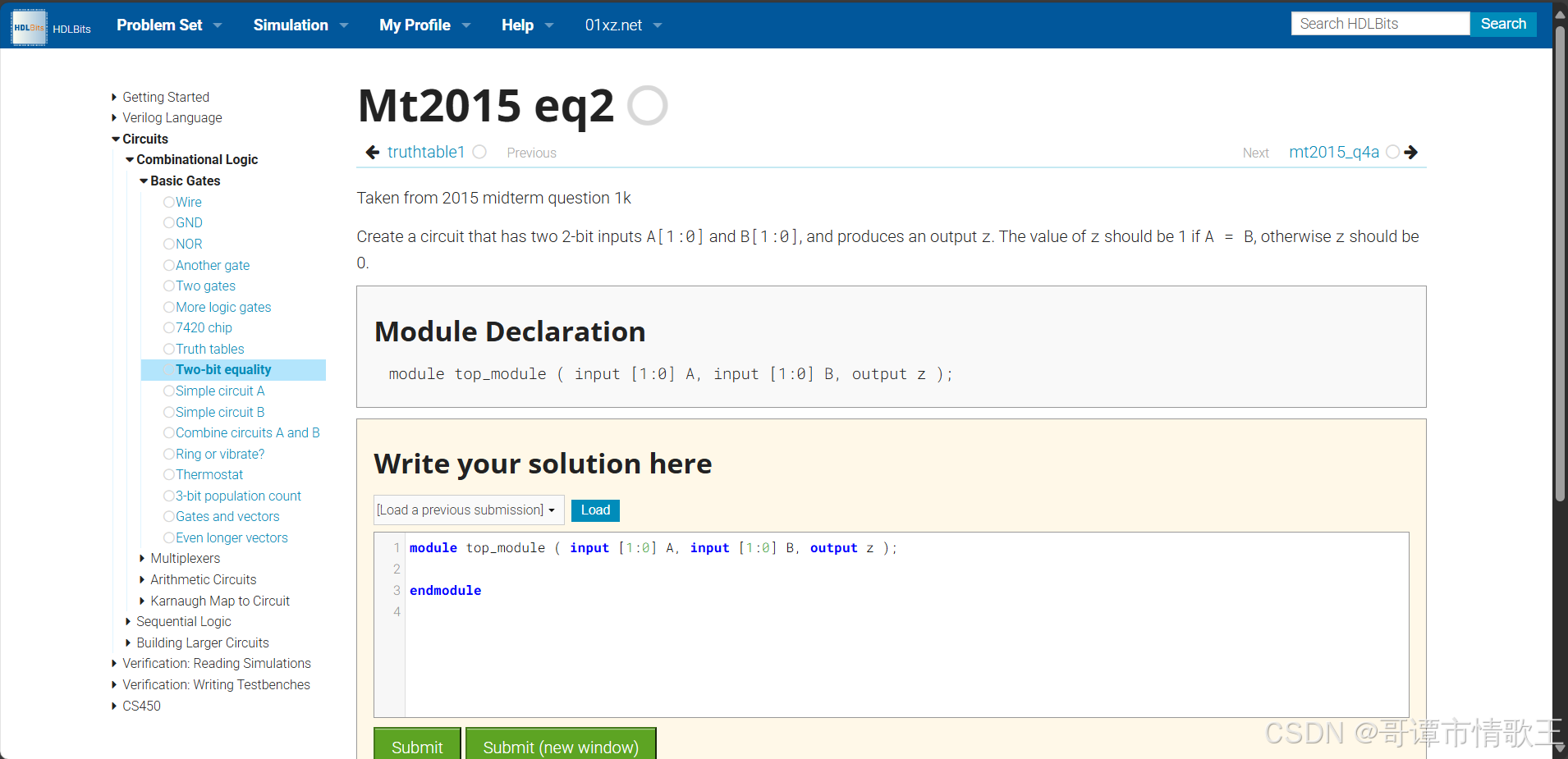

Two-bit equality(2位相等比较器)

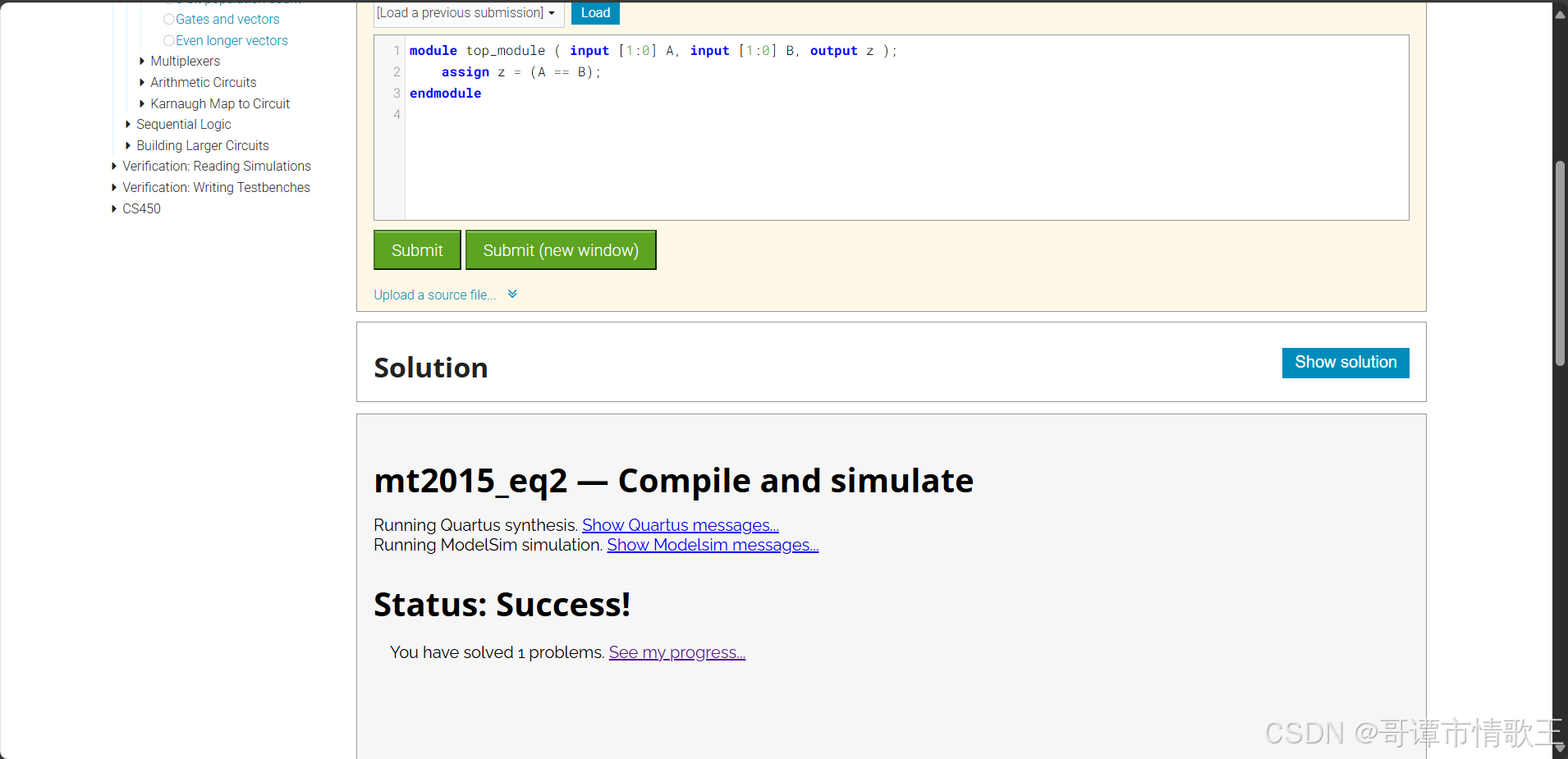

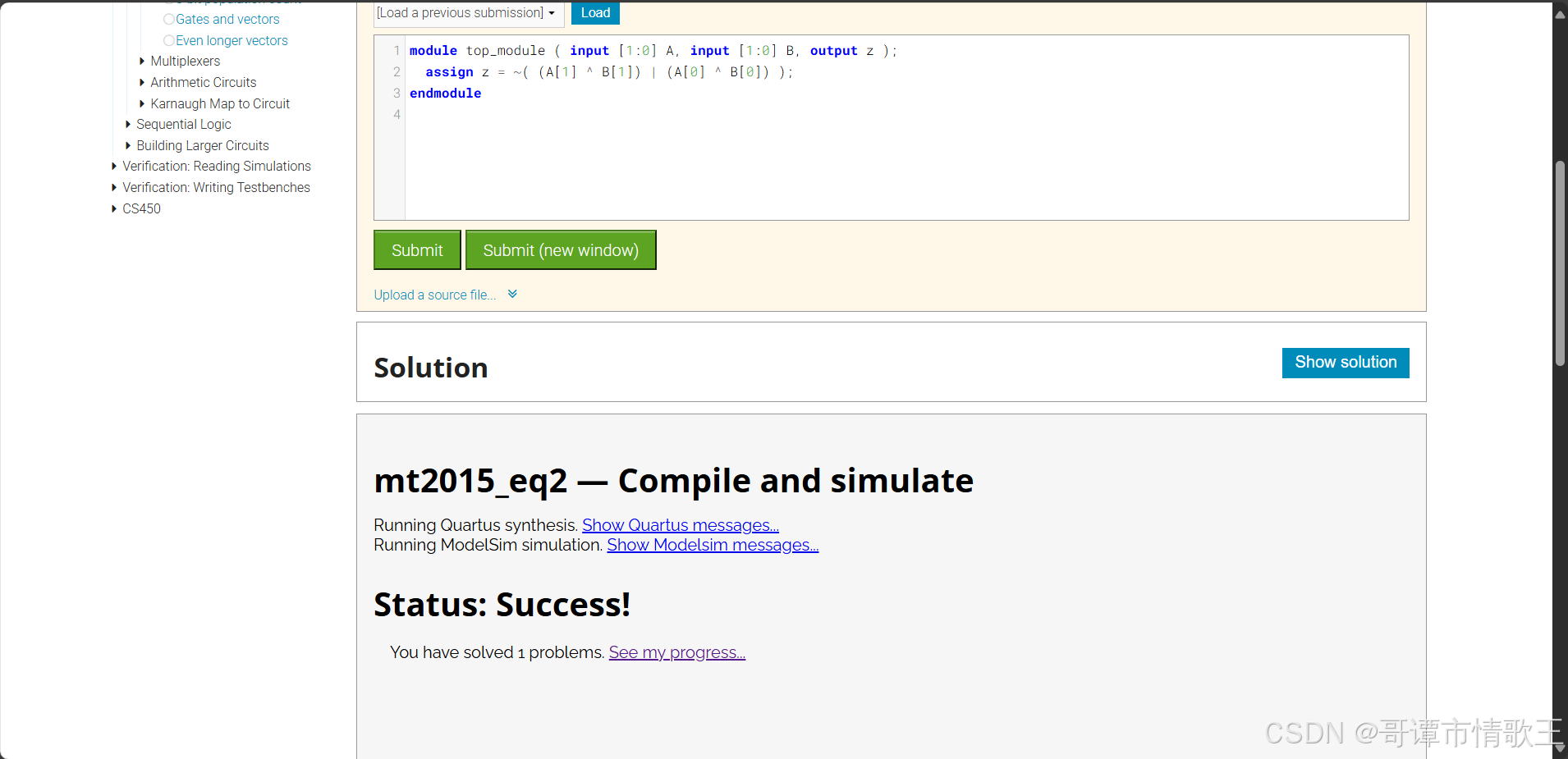

这是一个比较基础的练习

官方给出了A,B两个输入,Z为输出,输出Z满足如果 A == B,则 z = 1;否则 z = 0。

方法一(直接比较,因为Verilog 支持直接向量比较):

方法二(使用异或门):

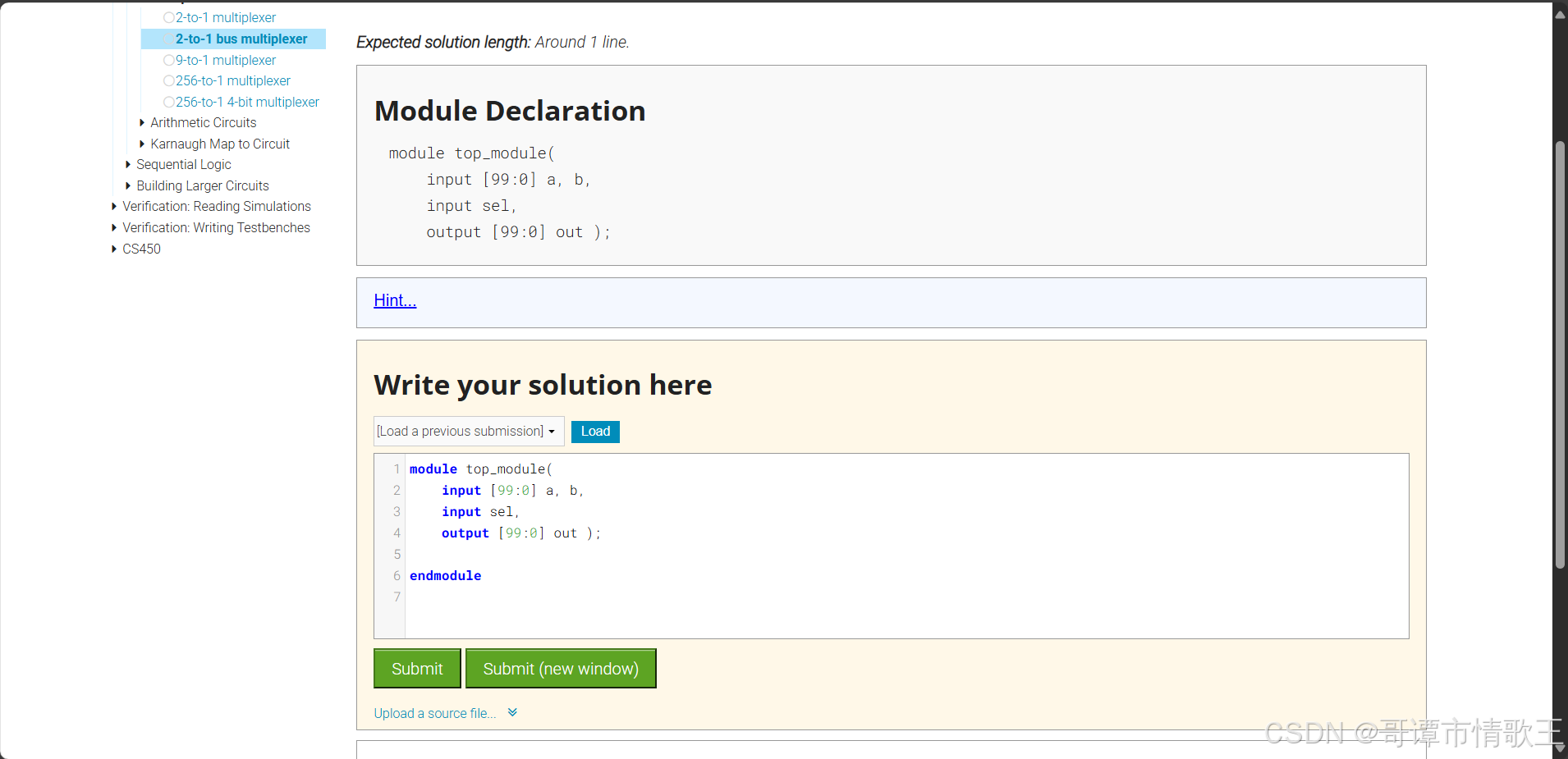

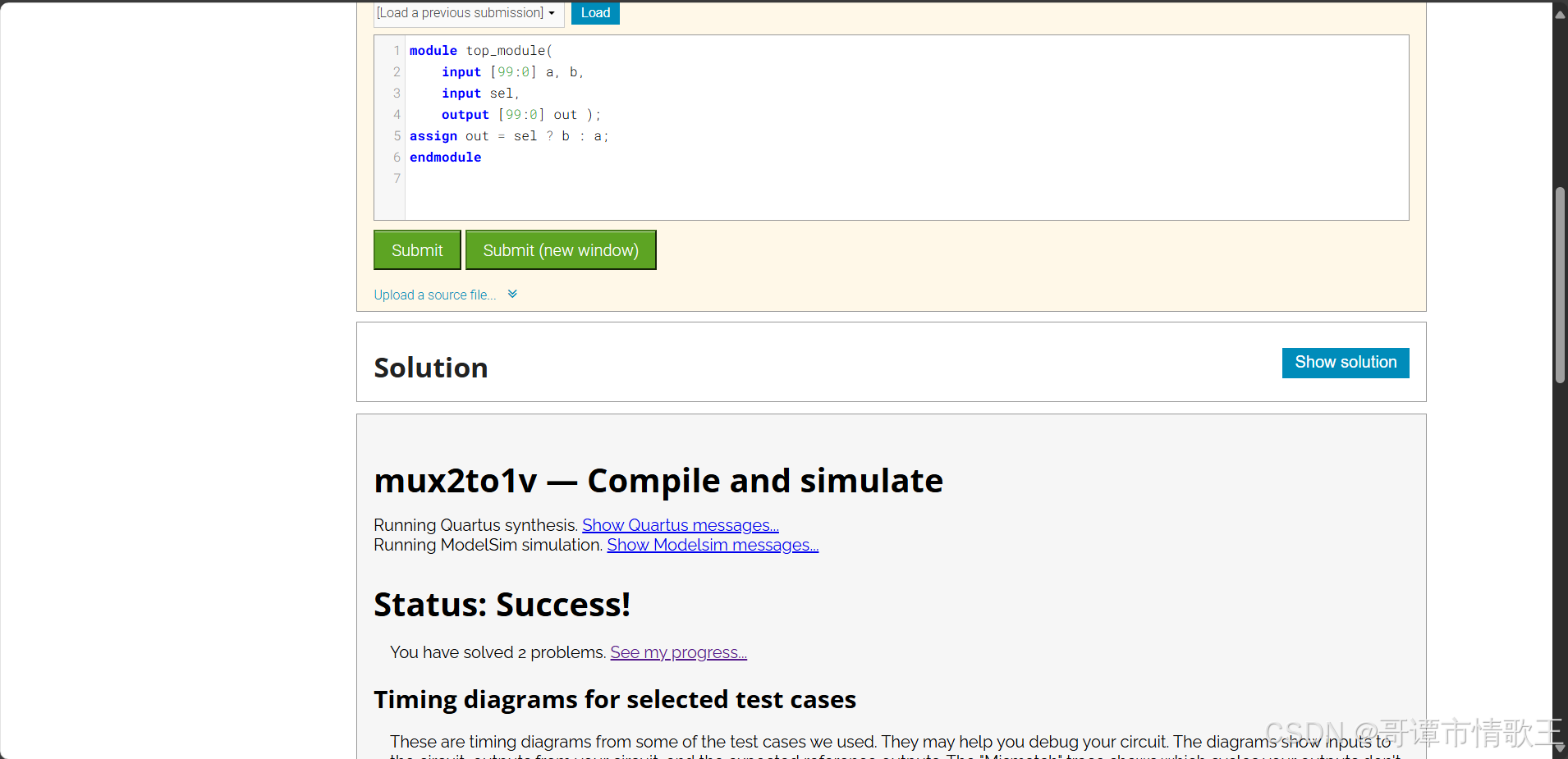

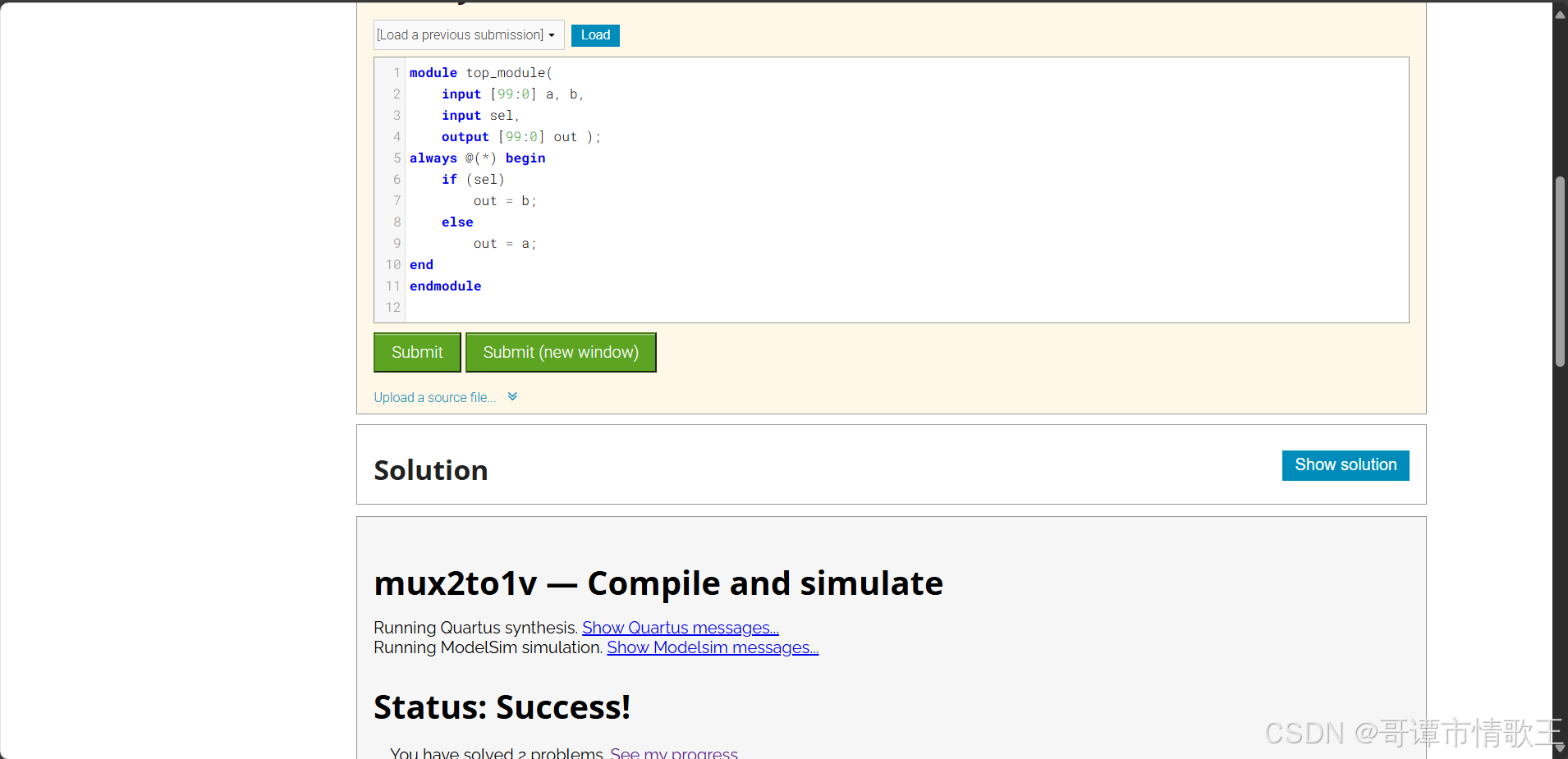

2-to-1 bus multiplexer(2选1总线多路复用器)

要求创建一个 100 位宽的 2 对 1 多路复用器。当 sel=0 时,选择 a。当 sel=1 时,选择 b。

方法一(使用条件运算符(?:)):

方法二(使用 if-else 语句)

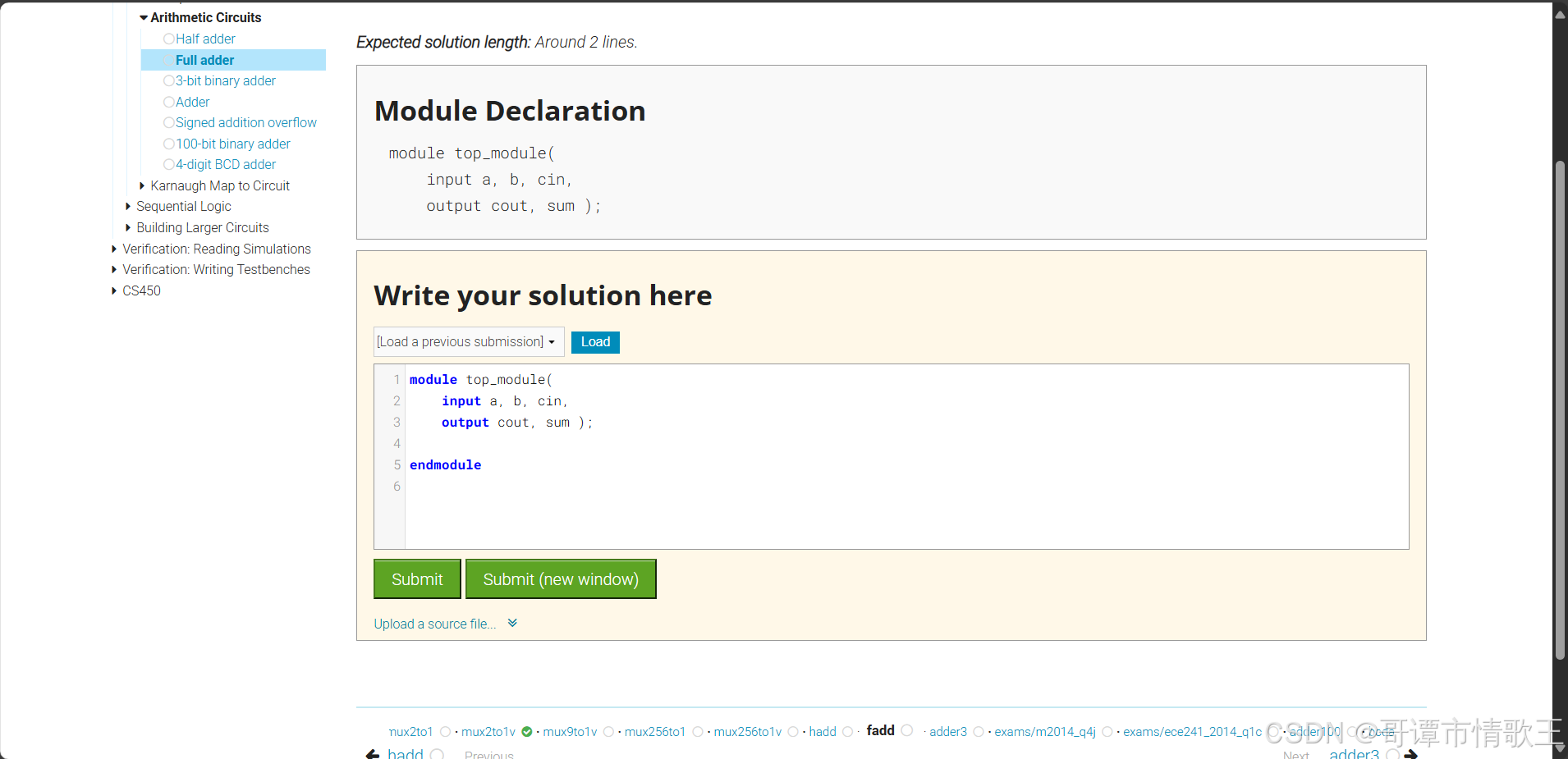

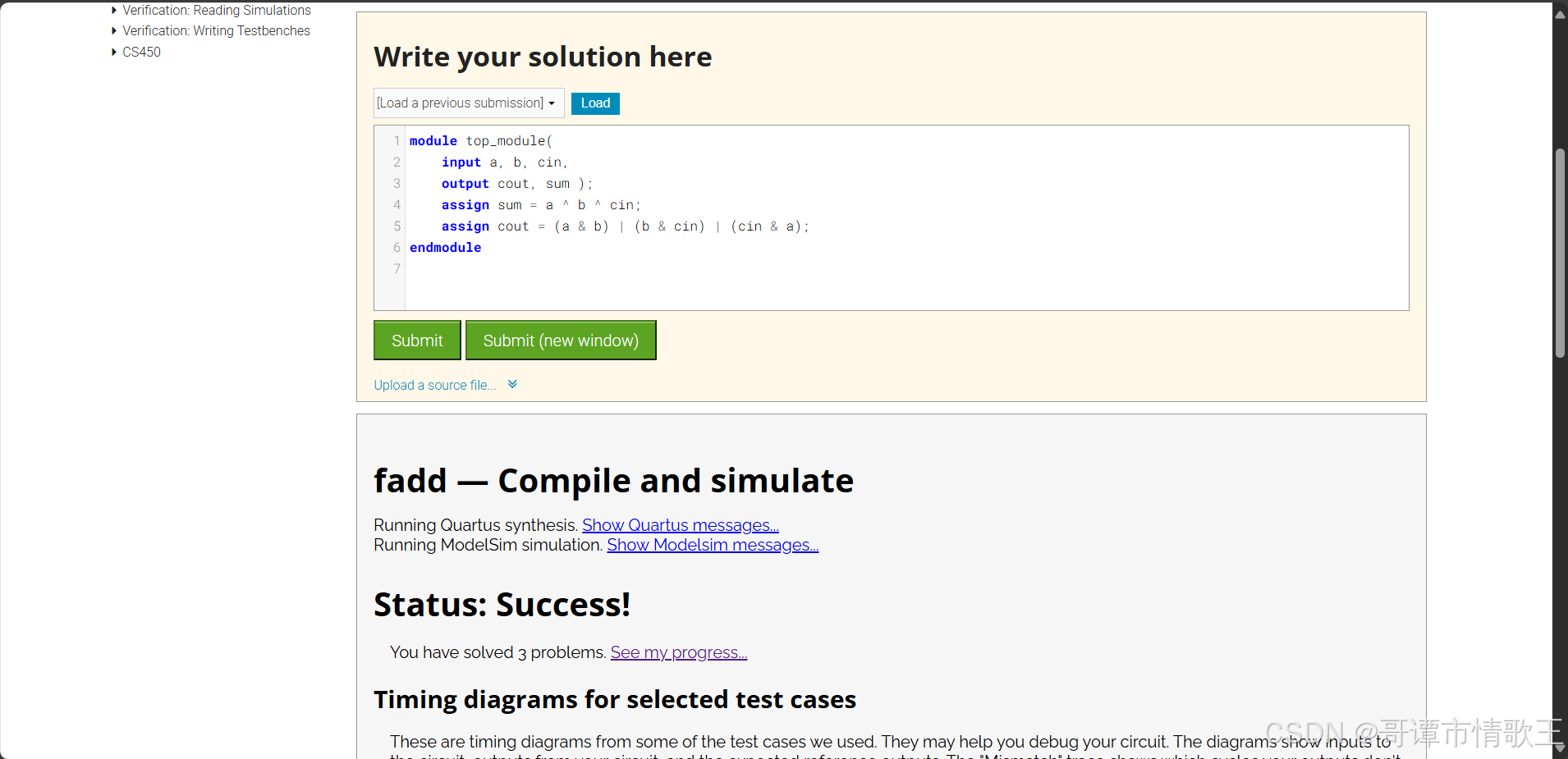

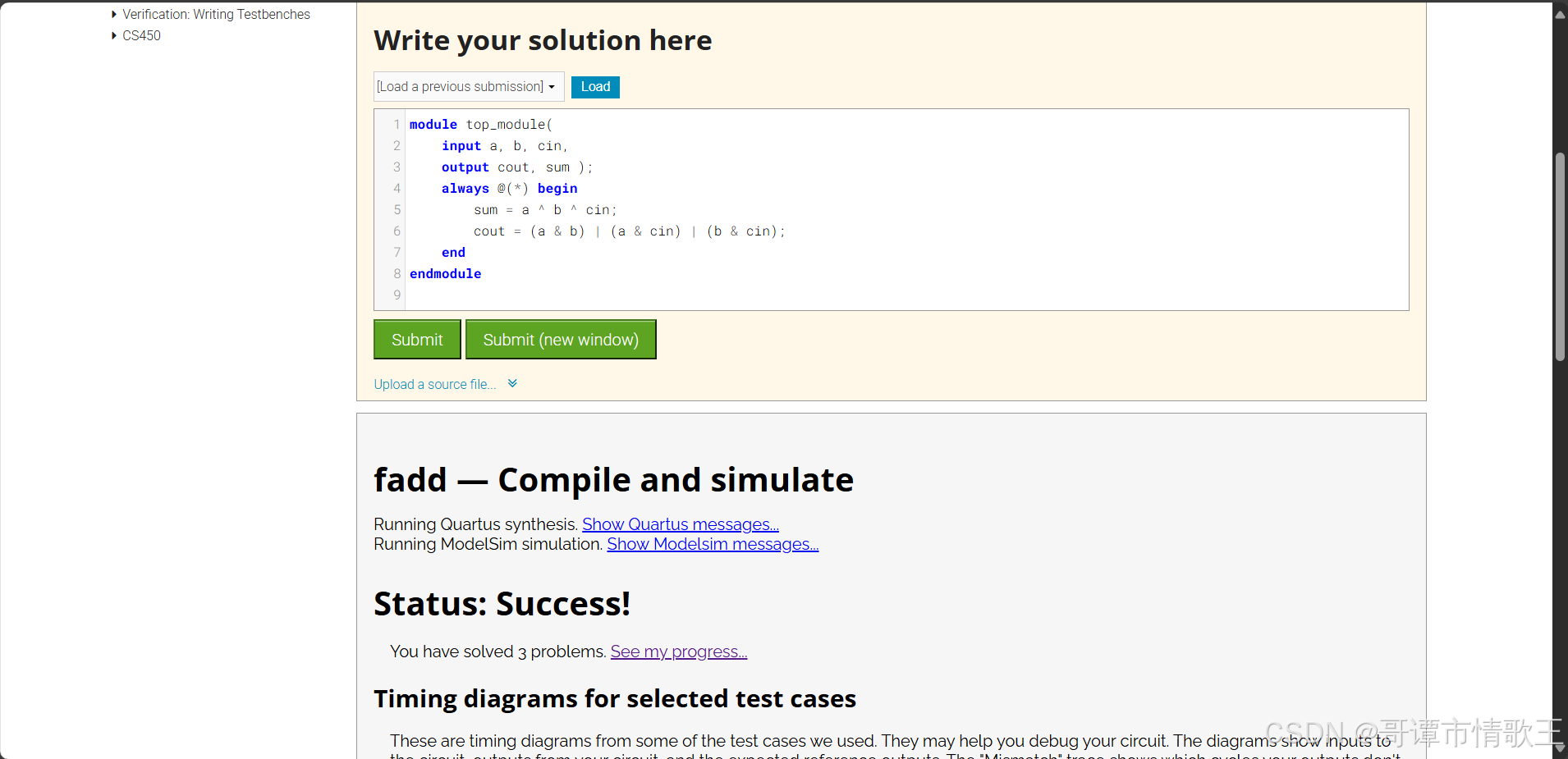

Full adder(全加器)

要求创建一个完整的加法器。全加器增加 3 位(包括 carry-in)并产生 sum 和 carry out。

方法一:

方法二(always):

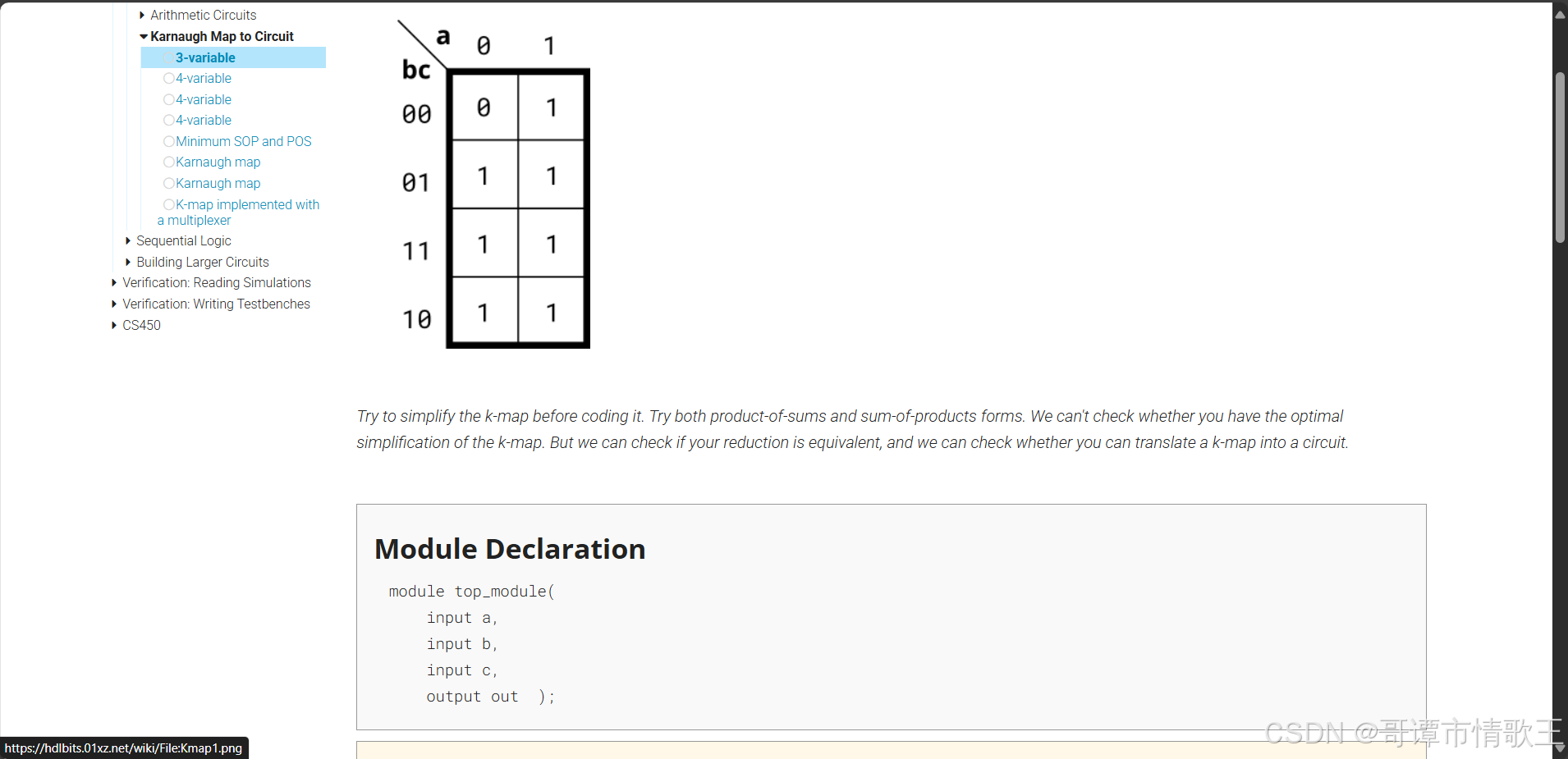

3-variable(3变量)

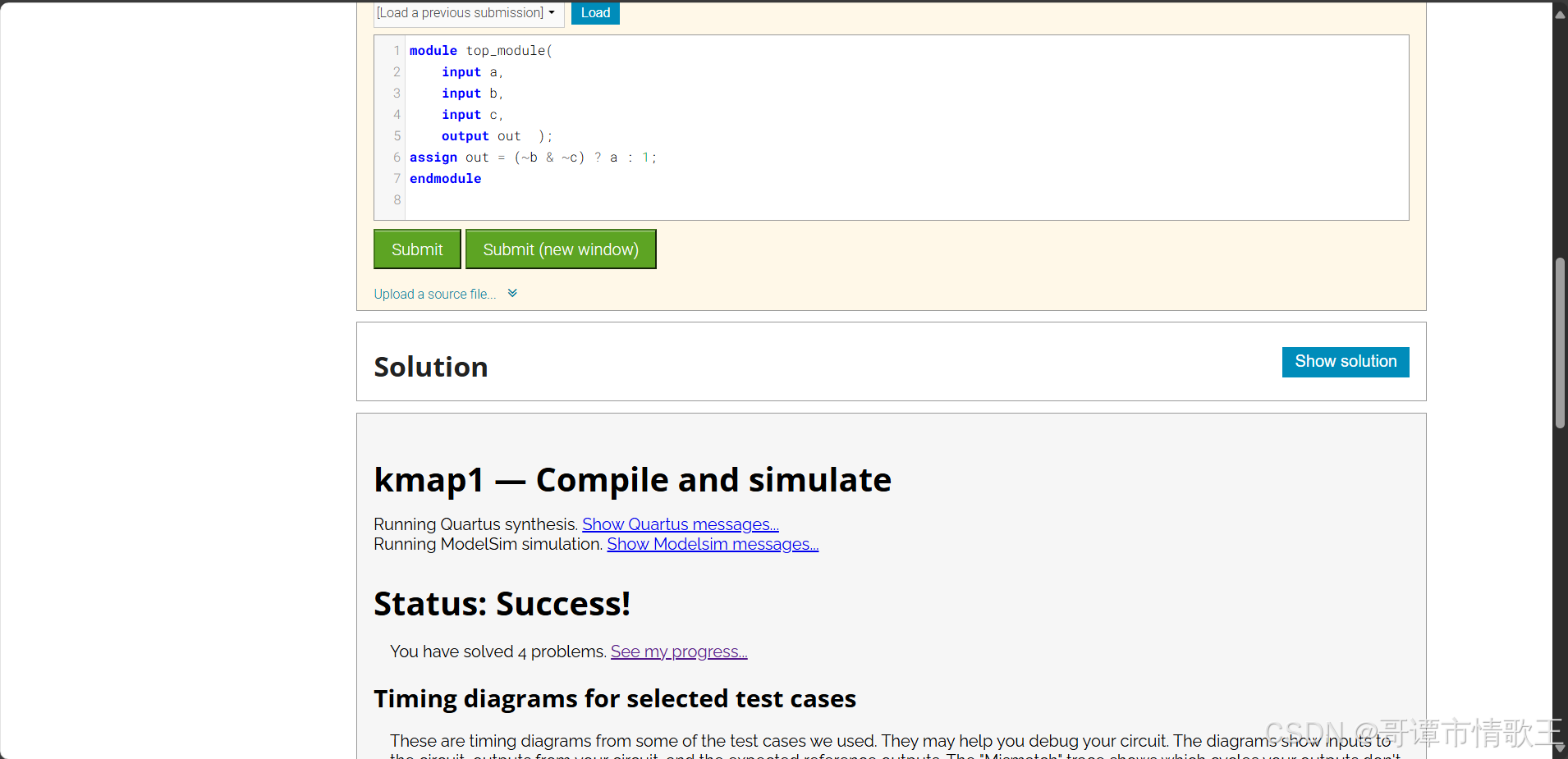

方法一:

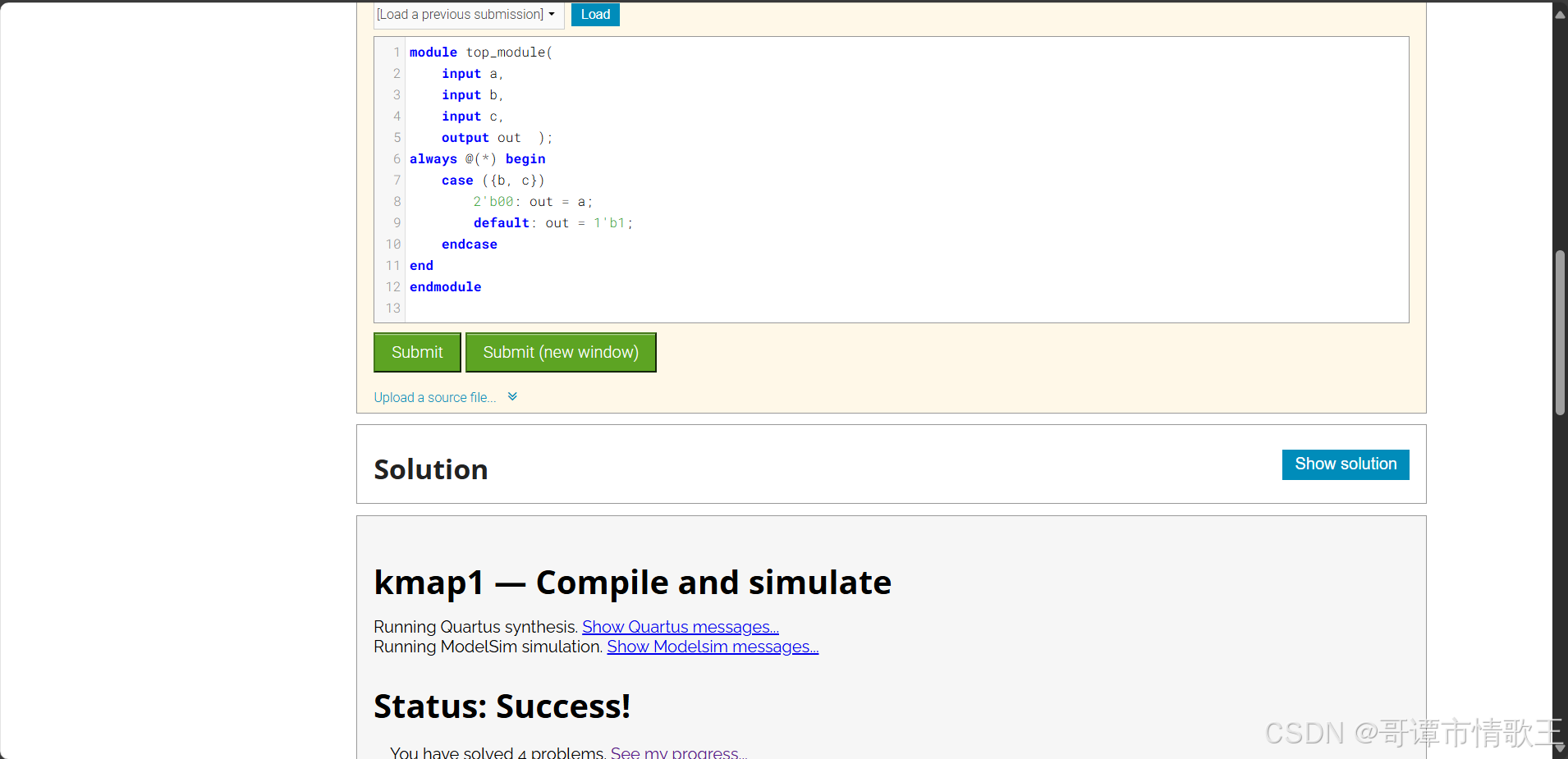

方法二(使用case):

总结

学习使人成长。

)