本文介绍一种基于XC7V690T 的在轨抗单粒子翻转系统架构;其硬件架构主要由XC7V690TSRAM 型FPGA芯片、AX500反熔丝型FPGA 芯片以及多片FLASH 组成;软件架构主要包括AX500反熔丝型FPGA对XC7V690T进行配置管理及监控管理,对XC7V690T进行在轨重构管理,XC7V690T通过调用内部SEMIP核实现对配置RAM 资源的自主监控和维护。

1. 硬件架构设计

某航天器通信机采用侧向层叠结构形式,共分为4个模块,由后至前依次为电源模块、射频模块、刷新模块及信号处理模块。电源模块接收航天器平台提供的一次电源,转换输出单机内其他模块正常工作所需要的各路电源。刷新模块包含了上电程序配置、健康监控和在轨重构的功能。射频模块接收天线经双工器发送过来的上行信号,通过混频、滤波、放大等转换成中频模拟信号,送给信号处理模块。射频模块还接收信号处理模块发送过来的中频模拟信号,经正交上变频、放大、滤波后转换成下行射频信号,经双工器后再通过天线发射出去。

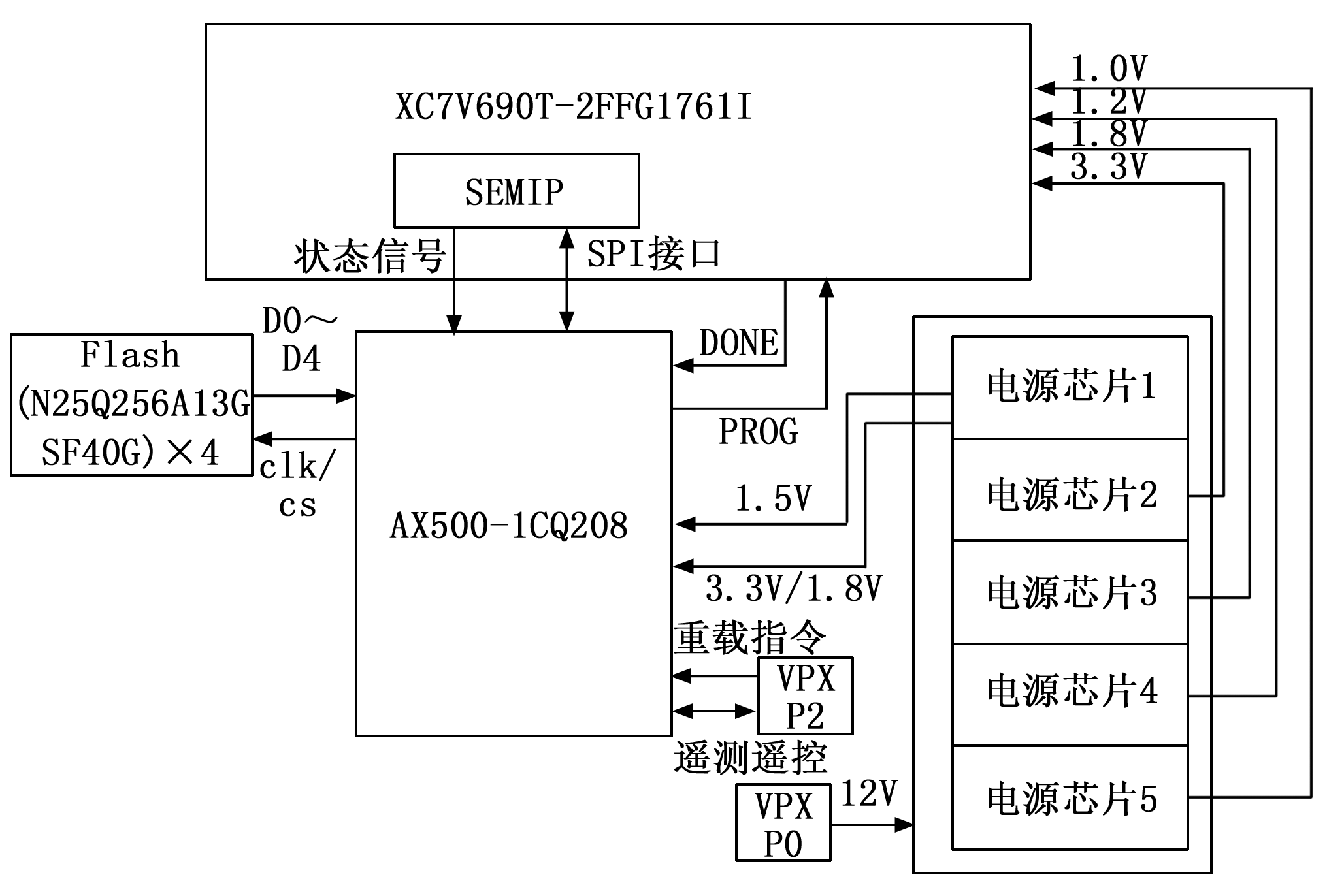

通信机信号处理及刷新模块设计框图如下图所示,采用了Xilinx公司的SRAM 型FPGAXC7V690T平台,主要具备以下功能:

1)接收射频模块发送过来的中频模拟信号,通过模数转换芯片采集后转换成12bit位宽的数字信号,传送给XC7V690T芯片进行信号处理;

2)将信号数据码流经XC7V690T芯片进行处理后,通过数模转换芯片进行转换形成中频模拟信号,发送给射频模块;

3)针对XC7V690T芯片的加载、刷新及重构功能。

针对该硬件架构,主要给出模块层和器件层的加固设计方案,针对XC7V690TFPGA 的加固设计主要由三部分组成:电源监控电路和控制电路、XC7V690TFPGA 内部调用的SEM 核和充当监控和维护核心的AX500FPGA。AX500FPGA除了需要监控XC7V690TFPGA配置和SEM工作状态,还要负责监测和控制XC7V690T 的供电情况,在识别故障后通过刷新和重上电等手段进行故障恢复。

该硬件架构由XC7V690T 芯片、反熔丝FPGA AX500芯片和4片512Mb容量的FLASH 存储器组成。其中:

1)XC7V690T芯片为需进行加固设计的FPGA 器件;

2)FLASH 用来存储XC7V690T芯片的配置文件;

3)AX500芯片的主要功能为读取FLASH 中的配置信息、上电加载和重载XC7V690T 芯片、监控SEMIP核的状态。AX500芯片与XC7V690T 芯片接口中的SPI-1为专用配置管脚,用来加载或重载FPGA。

2.软件架构设计

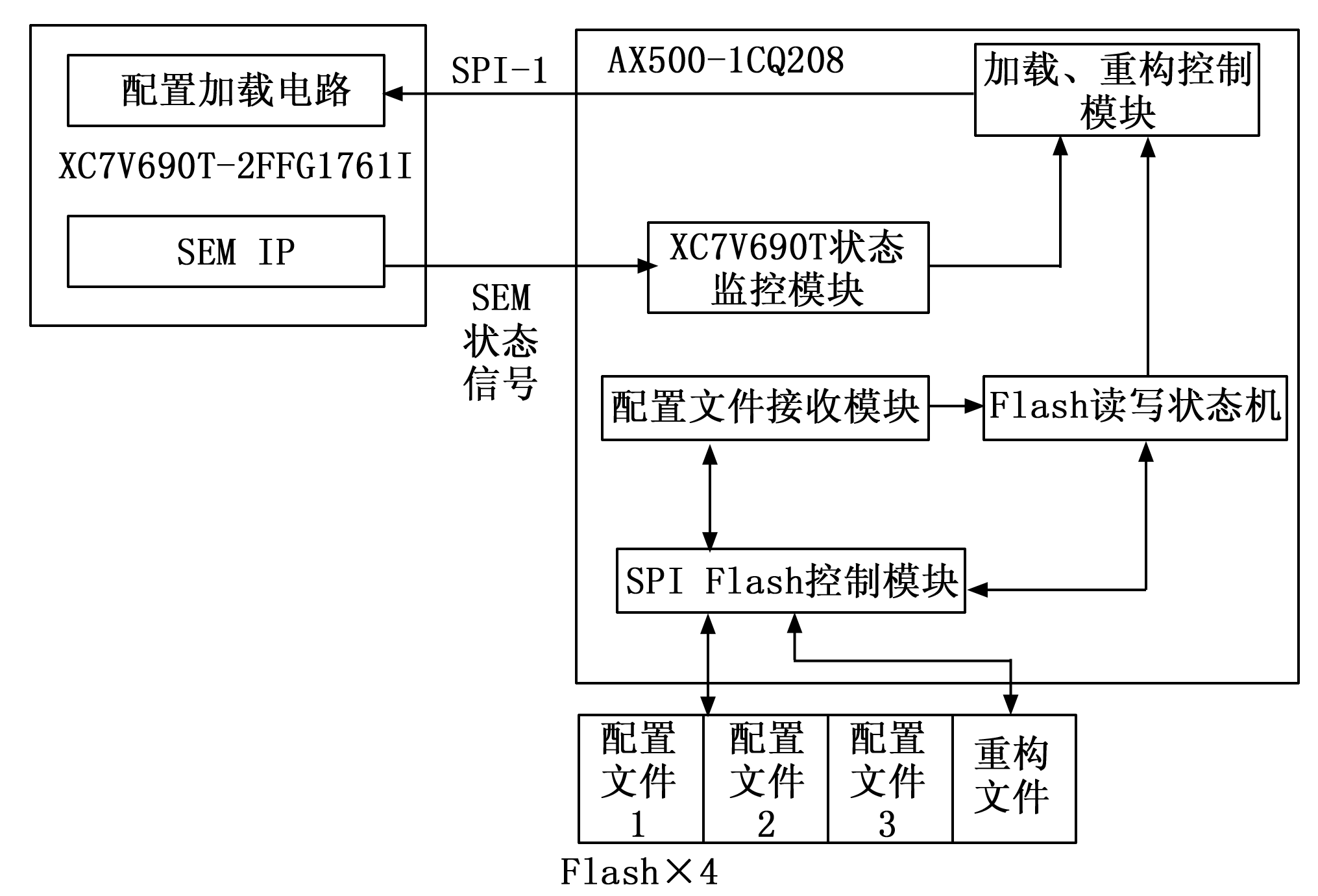

系统软件架构框图如下图所示。AX500芯片在上电时读取FLASH 中的配置信息, 通过SPI 接口加载目标XC7V690T芯片,加载完成后,监测XC7V690T 芯片的SEMIP核返回的状态信号,若检测到配置数据错误、SEMIP核自身发生错误或发生不可纠正的错误,则视需求读取FLASH 中的配置信息对目标XC7V690T 芯片进行重载操作。

2.1 XC7V690T配置管理和监控

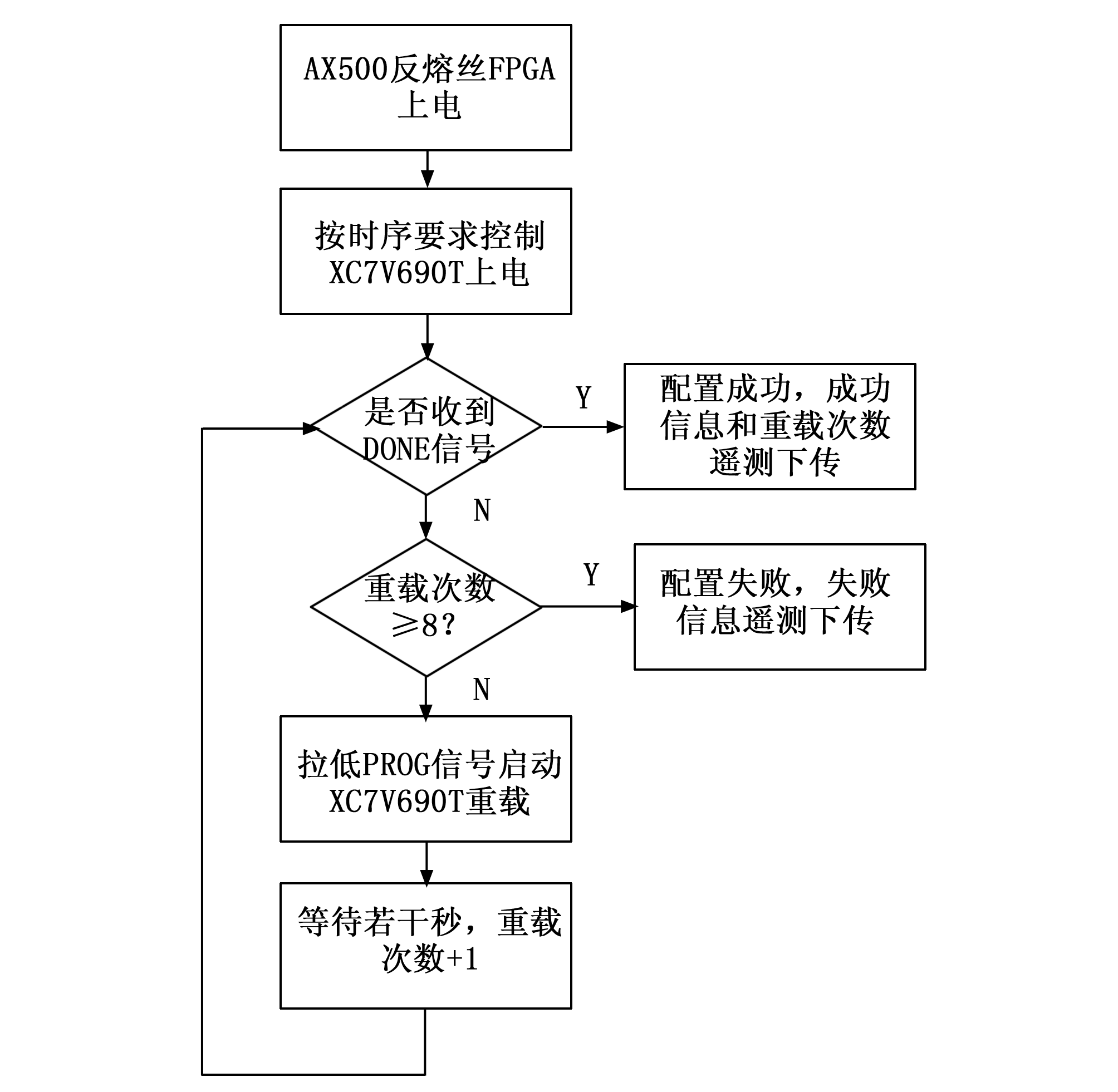

AX500反熔丝FPGA监控XC7V690T的配置状态,通过监控XC7V690T的DONE信号,若一定时间(外部须有时间跳线选择)内反熔丝FPGA 未收到DONE信号,表示XC7V690T未配置成功。此时,AX500反熔丝FPGA 拉低PROG信号对XC7V690T重新配置(热启动)。若热启动次数超过8次后仍未成功配置XC7V690T,表示无法进行板内重载,AX500反熔丝FPGA 通过遥测链路将模块故障信息下传地面。热启动重载流程图如下图所示。

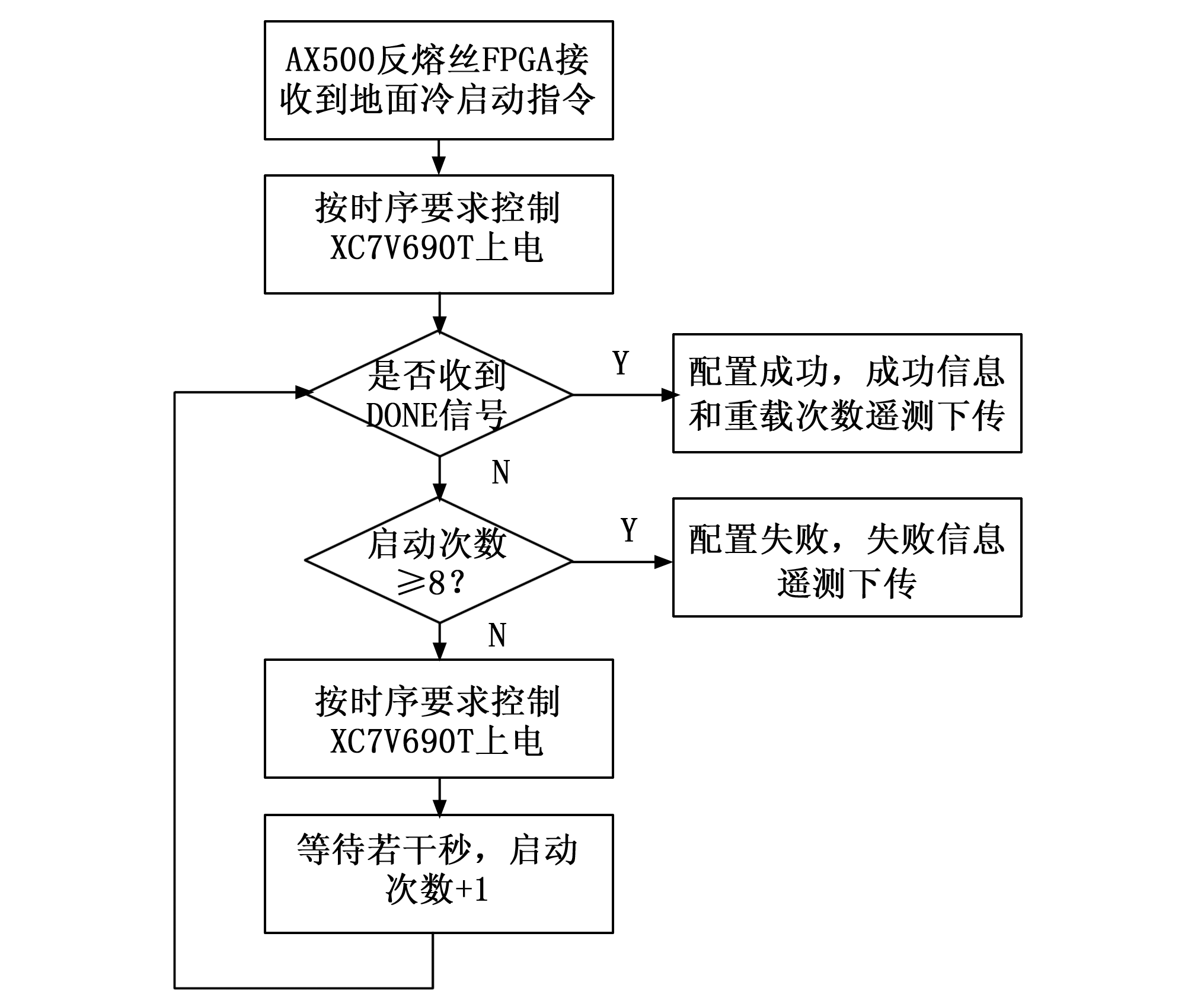

在热启动无法成功配置时,需要通过发送指令进行干预。该情况下,收到地面遥控指令,可以启动断电操作,通过断电重载进行恢复。若冷启动8 次仍未成功配置XC7V690T,AX500反熔丝FPGA 将其断电,并通过遥测链路将模块故障信息下传地面。冷启动加载流程图如下图所示。

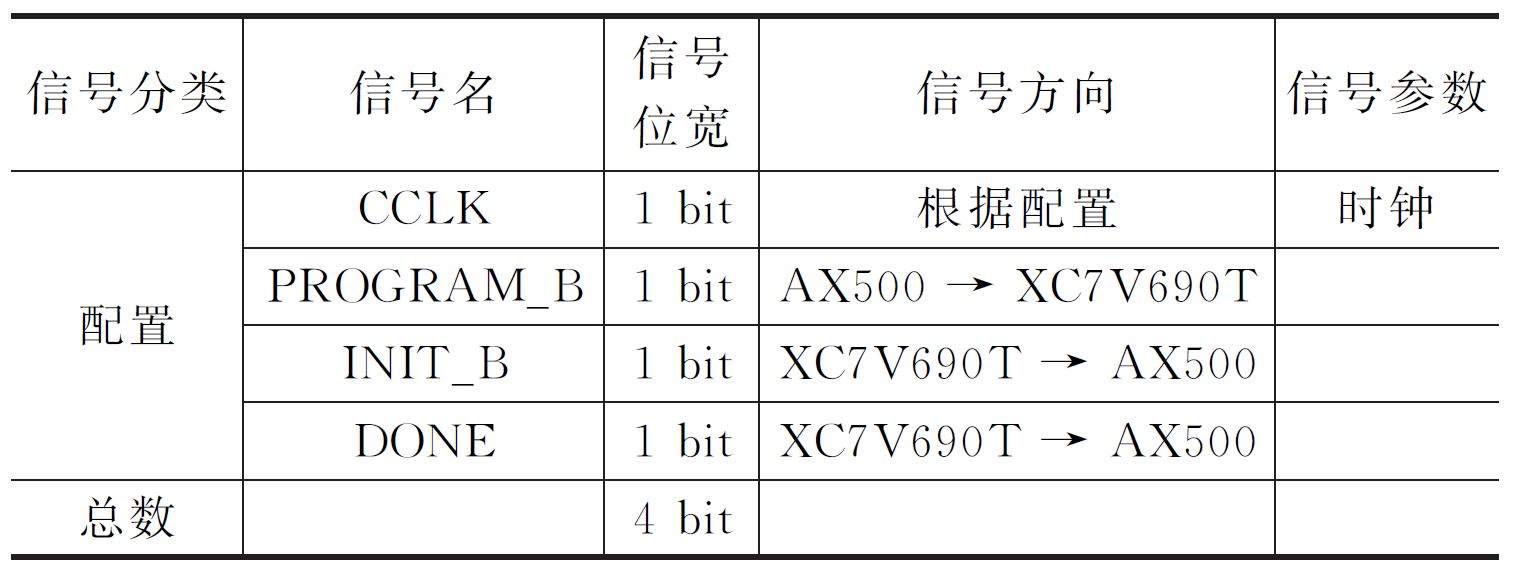

XC7V690T与AX500 配置监控接口具体信号如下表所示。

2.2 XC7V690TSEM 管理和监控

XC7V690T内部调用SEMIP核实现对配置RAM 资源的自主监控和维护。SEM 核利用片内的ICAP接口访问配置RAM 资源,并通过自带的差错控制编码(ECC,error correctingcode)和循环冗余校验码(CRC,cyclicredundancycheck)校验资源识别发生翻转的配置RAM 位,并能进行自动修复。

该功能可以配置成3种模式。

1)修复模式:以ECC算法为基础,可以纠正所有的单比特软错误;

2)增强修复模式:以ECC和CRC算法为基础,能修复任意的单比特和相邻双比特的翻转软错误;

3)替换模式:能够修复任意多个比特错误。

SEM 通过片内ICAP接口访问配置RAM,而传统的回读刷新通过片外SelectMAP接口访问配置RAM,两种接口的时序效率相差不大,但是外部回读需要通过PCB 走线,还要考虑反熔丝FPGA 的频率限制,所以主频通常远低于FPGA内部ICAP频率,因而需要更多时间,这使得SEM的故障识别时间远低于外部的回读刷新。

同时,由于XC7V690TFPGA没有公开配置帧的结构,无法进行精确的局部刷新,而全局刷新耗时长,并且其中绝大多数的刷新操作没有实际意义,加固效率较低。SEM技术则能够通过局部刷新的手段,实现非常高效的故障恢复。

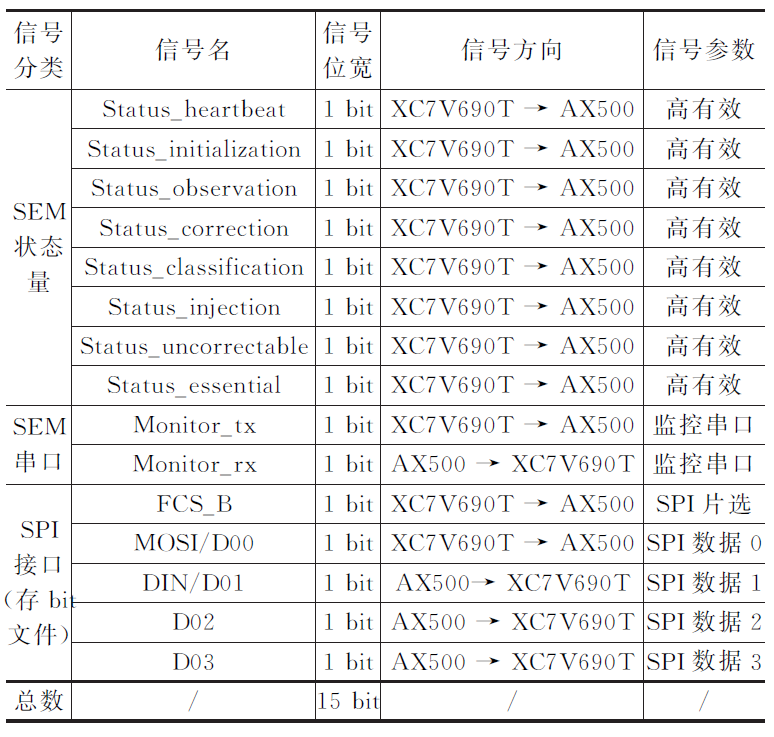

根据具体应用情况,SEMIP选择增强修复模式的纠错策略。XC7V690T与AX500SEM 监控接口具体信号如下表所示。

然而,SEM 本身仍然有可能会因为单粒子翻转而发生故障,虽然发生这种情况的概率要远远低于FPGA 本身发生单粒子翻转的概率,但仍然有必要针对这种情况设计故障恢复预案。通过反熔丝FPGA 直接监控SEM 的状态信息,可以判断SEM 功能是否正常工作,并在发生故障时通过重载(热启动)进行恢复。

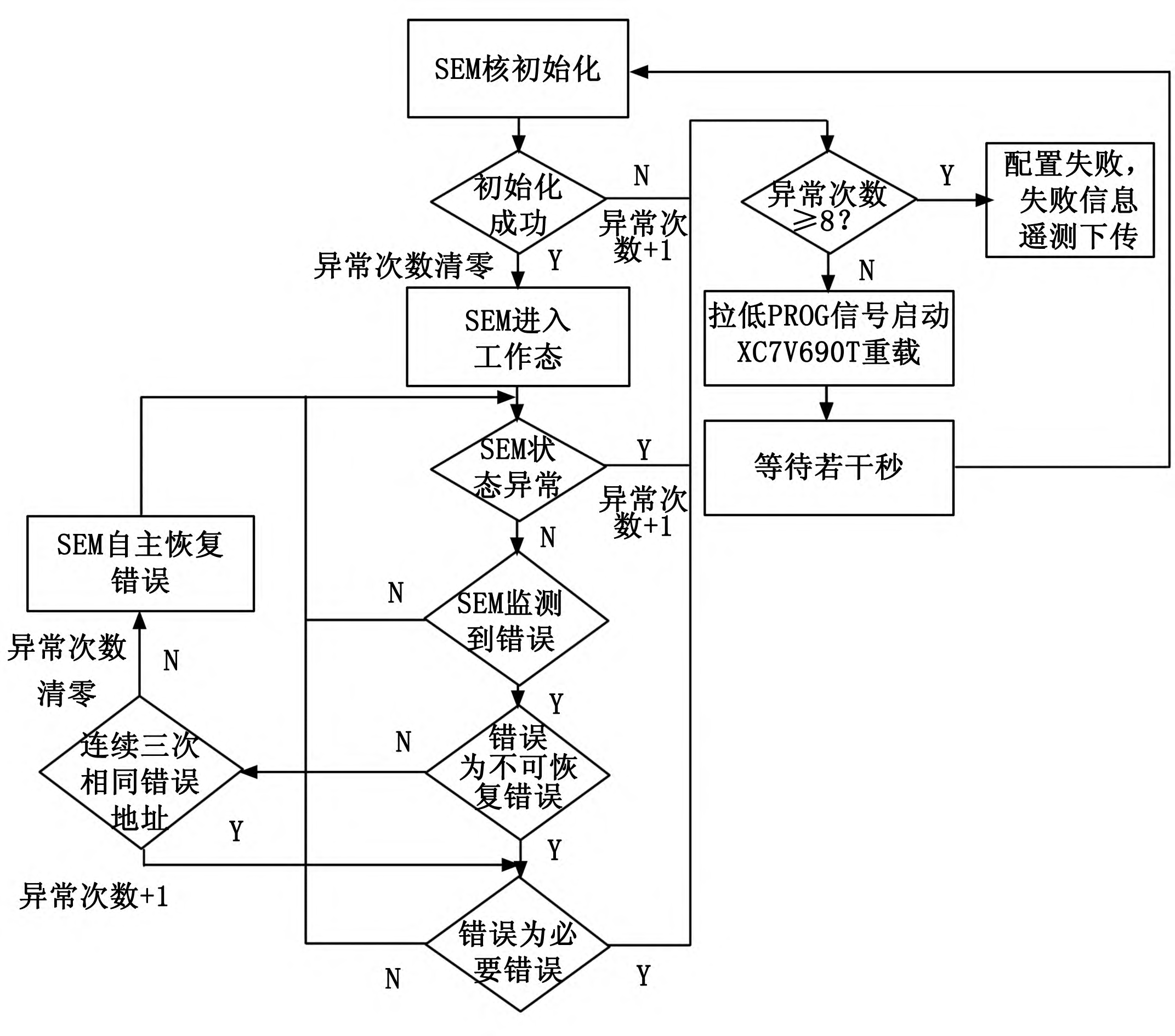

反熔丝FPGA需要启动重载操作的异常内容包括:

1)SEM 核未能成功完成初始化;

2)SEM 核在工作状态时发生异常;

3)SEM 核监测到不可恢复并且是必要比特错误;

4)SEM 核监测到连续三次相同地址的必要错误。

当出现上述情况时,反熔丝FPGA 尝试对XC7V690T进行重载(热启动)恢复,并且将异常计数+1。如果累积符合8次都未能恢复该异常,则反熔丝FPGA 停止重载恢复,并通过遥测链路下传相关故障信息。XC7V690TSEM 监控流程图如下图所示。

2.3 配置FLASH 控制及重构

采用3片FLASH 存储配置程序,用于配置文件三取二校验功能。为了进一步提升可靠性,新增1片FLASH 用于在轨重构。第4 片FLASH 用于在轨重构(第1~3 片FLASH 在轨期间不可进行写操作),重构数据流通信接口为异步RS422接口。

XC7V690T输出至反熔丝FLASH 的访问接口SPI,用于访问bit配置文件。而反熔丝FLASH 则需要维护4片SPI型FLASH。当XC7V690T 需要访问自己的配置FLASH 时,反熔丝FPGA会通过SPI接口发来的请求,反熔丝FPGA解析SPI指令和地址,并根据当前的配置模式,选择对4片SPIFLASH 进行操作。

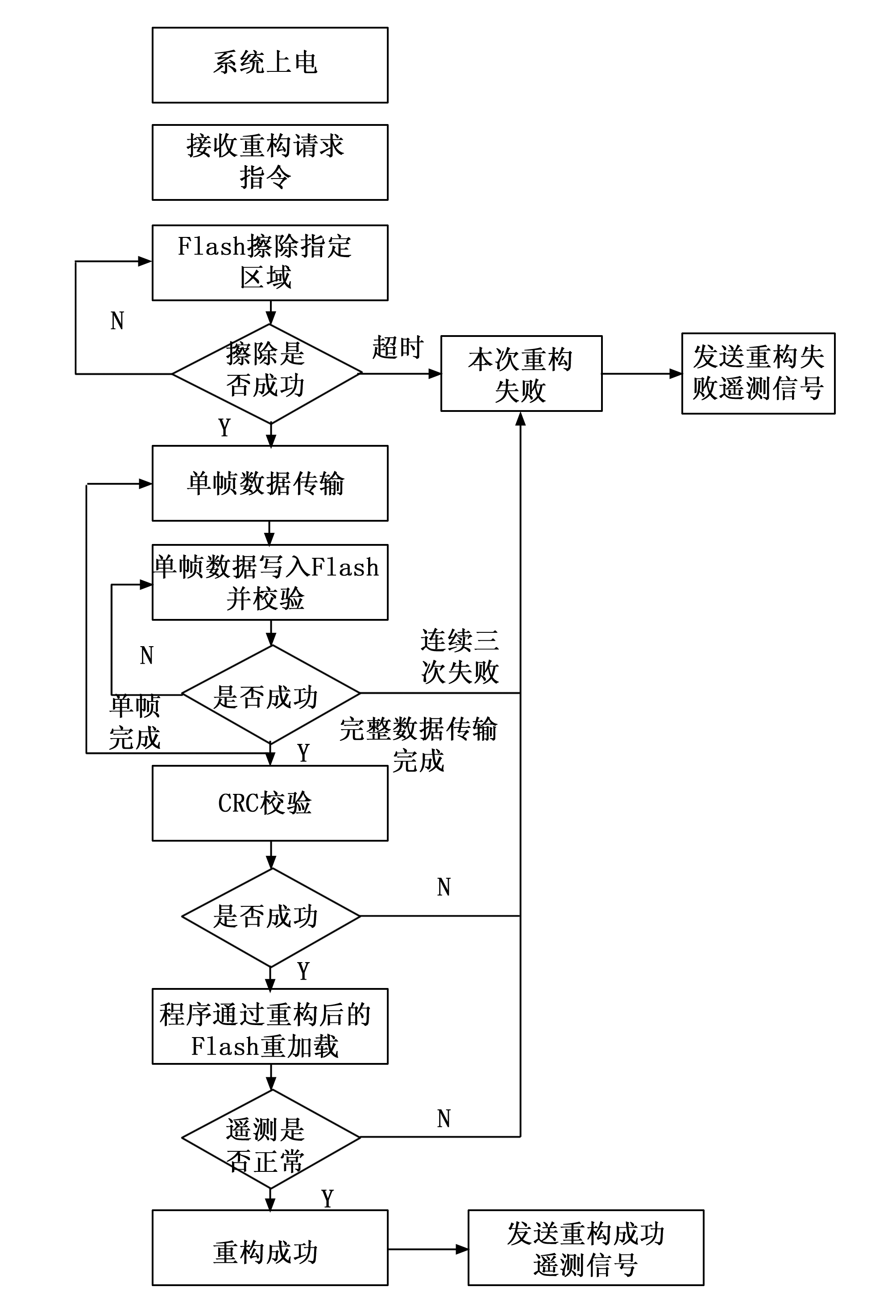

在轨重构工作流程设计如下:

1)地面发送遥控指令,请求重构,并告知重构区域(FLASH 内存空间内的首地址及长度)。

2)单机收到指令后对目标FLASH 中的对应区域进行擦除操作,擦除完成后发送遥测数据告知擦除完成,若超过指定时间后擦除仍未完成,则判定擦除失败,FLASH 中该部分区域失效。

3)单机通过异步RS422接口接收重构数据流,每接收一帧(帧长与FLASH 芯片的页长度相符)数据,写入FLASH 中,并根据接收到的CRC 值对FLASH 中的该帧数据进行校验,如校验通过,则发送校验通过信号,请求接收下一帧数据,反之,则反馈校验失败信号。数据发送方收到失败信号后重新发送该帧数据,如连续收到三次失败信号,则跳出本次重构流程。

4)当单机收到整个程序的校验指令和校验CRC值时,表示完整数据流已传输完毕,单机启动整个程序的CRC校验,校验失败则表示本次重构失败,反之,则复位FPGA芯片,通过重构后的FLASH 芯片重新加载程序,如遥测参数正常,方可判定为本次重构有效,单机通过遥测接口反馈该次重构结果(成功/失败)。

重构流程示意图如下图所示。

)

: 在windows系统上部署项目2)